Document

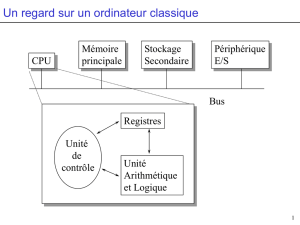

LE PROCESSEUR

1.1. Description de la fabrication d'un processeur

1.2. L'architecture d'un processeur

1.2.1. Schéma synoptique de l'architecture d'un Intel 386

1.2.2. L'unité d'anticipation Prefetcher

1.2.3. L'unité de pagination Paging Unit et Segmentation unit

1.2.4. L'unité d'interface Bus Control

1.2.5. L'unité de décodage Decode and sequencing et Instruction Decoder

1.2.6. L'unité de contrôle

1.2.7. L'unité de test de protection Protection Test Unit

1.2.8. Les registres

1.2.9. L'unité Arithmétique et Logique

1.2.10. L'unité de Contrôle

1.3. Evolution de l'architecture des processeurs

1.3.1. Composants de bases : gravure, fréquence, CICS, RISC, cache, pipeline

1.3.2. Le concept de pipeline

1.3.2.1. Description des 5 étages du pipeline du i486 et du Pentium

1.3.3. L'architecture superscalaire, cas du Pentium

1.3.3.1. Pipeline et Superscalaire

1.3.3.2. Schéma synoptique du Pentium

1.3.3.3. Le bus d'adresses

1.3.3.4. Le cache intégré de niveau 1 = L1

1.3.3.5. L'unité de calcul

1.3.3.6. Fréquence et tension d'alimentation du CPU

1.4. Les instructions MMX et la technique SIMD du Pentium MMX

1.4.1. SIMD : Single Instruction Multiple Data

1.4.2. Schéma synoptique du Pentium MMX

1.4.3. Structure du pipeline du Pentium MMX

1.5. Prédiction de branchement et exécution spéculative avec le Pentium Pro

1.5.1. Le Pentium Pro

1.5.2. Prédiction de branchement et exécution spéculative.

1.5.3. Schéma synoptique du Pentium Pro

1.5.4. Comparaison d'architecture entre le Pentium et le Pentium Pro

1.6. L'architecture du Pentium II et du Pentium II Xéon

1.6.1. Le Pentium II et l'architecture D.I.B.

1.6.2. Evolution des caractéristiques avec le Pentium II Xéon

1.6.2.1. Bus de mémoire cache de niveau 2 à 400 MHz ou 450 Mhz

1.6.2.2. Architecture à deux bus indépendants

1.6.2.3. Bus système à 100 MHz

1.6.2.4. Bus système à transactions indépendantes

1.6.2.5. Mémoire cache de niveau 2 à correction d'erreurs

1.6.2.6. Mode multiprocesseur symétrique SMP

1.6.2.7. Exécution dynamique

1.6.2.8. Prédiction de branchements multiples

1.6.2.9. Analyse du flux de données

1.6.2.10. Exécution spéculative

1.6.3 Fonctions d'administration évoluées du Pentium II Xéon

1.6.3.1. Capteur thermique

1.6.3.2. Détection et correction des erreurs (ECC)

1.6.3.3. Contrôle fonctionnel des redondances

1.6.3.4. Bus d'administration du système

1.7. Comparaison des architectures INTEL et AMD

2. Caractéristiques des processeurs INTEL

2.1. Famille des 4004 au 8088

2.2. Famille des 80286 au 80386

2.3. Famille des 80486

2.4. Famille des Pentium

2.5. Famille des Pentium II et Pentium II Xeon

2.6. Famille des Celeron

2.6.1. La famille des Celeron pour Mobile

2.7. Famille des Pentium III et Pentium III Xeon

2.7.1. La famille des Pentium III Ultra Low Voltage, Low Voltage et Mobile

2.8. Famille des Pentium IV et Pentium IV Xeon

2.9. Famille des Itanium 64 bits

3. Caractéristiques des processeurs AMD

3.1. Description du codage des CPU

3.2. Famille des Am386

3.3. Famille des Am486

3.4. Famille des Am5x86

3.5. Famille des AMD K5

3.6. Famille des AMD K6

3.6.1. Famille des AMD K6-2

3.6.2. Famille des AMD K6-2E et AMD K6-2E+

3.7. Famille des AMD K6-III et AMD K6-IIIE+

3.8. Famille des AMD Duron

3.9. Famille des AMD Athlon

3.10. Famille des AMD Athlon XP

4. Performances des processeurs

4.1. Performances des processeurs INTEL

4.1.1. Performances des Pentium

4.1.2. Performances des Pentium Pro

4.1.3. Performances des Pentium II

4.2. Performances des processeurs Cyrix

4.3. Performances des processeurs AMD

5. Caractéristiques des supports de processeur, sockets et slots

6. Format des différents boîtiers de processeur

6.1. PGA = Pin Grid Array

6.2. PQFP = Plastic Quad Flat Pack

6.3. SQFP = Shrink Quad Flat Pack

6.4. TQFP = Thin Quad Flat Pack

6.5. PBGA = Plastic Ball Grid Array

6.5.1. Plastic Ball Grid Array 1

6.5.2. Plastic Ball Grid Array 2

6.6. SPGA = Ceramic Staggered Pin Grid Array

6.7. PPGA = Plastic Staggered Pin Grid Array

6.8. HL-PBGA = Thermally Enhanced, Plastic Ball Grid Array

6.9. SECC = Single Edge Contact Cartridge

6.9.1. SEC Slot1 = Single Edge Contact Cartridge

6.9.2. SEC Slot2 = Single Edge Contact Cartridge

6.10. SEC = Single Edge Contact

6.11. SECC2 OLGA et PLGA = Single Edge Contact Cartridge

6.12. FC-PGA = Pin Grid Array

6.12.1. Support FC-PGA1

6.12.2. Support FC-PGA2

6.12.3. Différence entre FC-PGA1 et FC-PGA2

6.13. PAC418 = 418 Pin Array Cartridge

6.13.1. PAC418 Dessus

6.13.2. PAC418 Dessous

1.1. Description de la fabrication d'un processeur

Un MICROPROCESSEUR contient plusieurs millions de composants électroniques et intègre

plusieurs milliers de transistors. La fabrication est le résultat du transfert d'un schéma électrique

sur une plaquette de silicium. Ce schéma, dont le détail est invisible à l'œil nu, possède jusqu'à

vingt couches superposées sur une seule plaquette pour former le circuit final. Ce circuit est à son

tour enfermé dans un boîtier en céramique ou en plastique, puis relié aux broches pour former un

microprocesseur. La matière première est constituée d'atomes de silicium qui se fondent en un

lingot dont la pureté est rigoureusement contrôlée. Ce dernier est alors découpé en galettes (wafer

en anglais) d'épaisseur uniforme. Celles ci sont ensuite polies jusqu'à ressembler à de minuscules

miroirs.

1 Le procédé de transfert du dessin d'un circuit intégré sur la galette reprend celui qui est employé

en photographie. Tout d'abord, le dessin est reproduit sur une plaque recouverte de chrome, le

photomasque, qui fera office de négatif. Le fait de soumettre la galette à de hautes températures en

atmosphère régulée crée une couche de dioxyde de silicium à la surface de la galette. Cette

pellicule, dont les propriétés électriques diffèrent de la couche sous-jacente, est recouverte d'un

composant photosensible.

2 Pour transférer le dessin du circuit sur la galette, on expose celle-ci à la lumière au travers du

photomasque utilisé comme négatif.

3 A la suite de cette opération, la partie exposée est enlevée avec un développeur chimique. Le

dessin du circuit se retrouve alors reproduit dans l'élément photosensible.

4 La galette est ensuite placée dans une atmosphère de gaz actifs qui enlève la partie oxydée non

protégée par l'élément photosensible.

5 L'étape suivante est l'implantation d'ions. Des éléments chimiques, électriquement actifs, les

dopants, sont implantés dans les couloirs du circuit. Cela génère des régions (ou puits) qui

emmagasinent des charges électriques et contrôlent le flux de courant (des électrons). La

connexion de ces puits au reste du circuit est réalisée par un dépôt de pellicules métalliques

microscopiques parfois de l'aluminium. Le procédé photosensible est employé pour ne laisser

cette pellicule métallique qu'en certains endroits. Le résultat produit une couche d'un circuit

intégré qui, suivant sa complexité, en possédera jusqu'à vingt superposées sur la plaquette. Celle ci

sera insérée au sein d'une coquille de céramique ou de plastique. La dernière étape consiste à relier

ce circuit aux broches du microprocesseur.

1.2. L'architecture d'un processeur Intel

1.2.1. Schéma synoptique de l'architecture d'un Intel 386

1.2.2. L'unité d'anticipation Prefetcher

Les instructions à exécuter arrivent dans l'unité d'Anticipation (Prefetch Unit) via le bus. Cette

unité conserve la liste des instructions à exécuter puis demande à l'unité d'Interface Bus (Bus

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

1

/

54

100%