proc

P.GRANDADAM BTS INFORMATIQUE DE GESTION page 1

Lyc Bonaparte Toulon TECHNOLOGIE DES COMPOSANTS D’UN ORDINATEUR poly nov 2007

0 REFERENTIEL DU BTS

0.1 CAPACITES ATTENDUES

- DEV+RES Caractériser et décrire les composants d'un ordinateur.

- DEV+RES Identifier les technologies et normes relatives aux composants d'un ordinateur.

- RES Maîtriser les systèmes de numération et de codification de l'information.

- RES Évaluer et comparer les technologies et normes relatives aux composants d'un ordinateur.

0.2 LE CONTENU DES COURS

- Processeurs de traitement.

- Processeurs spécialisés.

- Mémoires.

- Bus.

- les cartes filles

- les périphériques

- les réseaux

1 LE MICRO-PROCESSEUR

1.1 DEFINITION PROCESSEUR-MICRO-PROCESSEUR :

Un processeur est l’élément qui traite l’information (les données) en exécutant les instructions

contenues dans un programme.

Un Micro-Processeur est un processeur intégré sur une puce.(circuit intégré).

Un processeur donne un ordinateur, un micro-processeur donne un micro-ordinateur.

1.2 ROLE D’UN MICRO-PROCESSEUR :

Il décripte, interprète, exécute les instructions du programme en cours.

Il est composé essentiellement de deux unités :

L’unité de contrôle (control unit), ou unité de commande, qui décode et commande l'exécution des

instructions machine .

L'unité arithmétique et logique (UAL) qui traite les données (variables)

1.3 LA GAMME DES DIFFERENTS FABRICANTS:

INTEL : 8086, 80286, 80386, 80486,

Pentium, Pentium pro, Pentium II, Celeron, Pentium III,

Pentium 4, M, D, EE, Dotan , core2 duo

Xeon, Merced , Itanium,

AMD (Advanced Micro Devices) : 5K86, K6, K7, Duron, Athlon XP,

Athlon 64, 64 FX, 64 X2, turion, Sempron, Opteron

CYRIX : 6x86P166+...

MOTOROLA et IBM: 68040, Power Pc-G4

HP ( COMPAQ ( DIGITAL ) )

DIGITAL : Alpha 21164, Alpha 21264 (arrêt)

VIA : Eden-N

P.GRANDADAM BTS INFORMATIQUE DE GESTION page 2

Lyc Bonaparte Toulon TECHNOLOGIE DES COMPOSANTS D’UN ORDINATEUR poly nov 2007

1.4 un registre

Au cours du traitement, une instruction, une donnée, un résultat sera temporairement conservé dans un

élément de mémoire appelé REGISTRE (longueur de 1 à 2 mots mémoire : …………………).

exemples : registre instruction, adresse, index, compteur ordinal, etc ....

nota : une machine à registres (la quasi-totalité des machines actuelles) est qualifiée de "MACHINE DE

VON NEUMANN", du nom du créateur du principe.(1950)

1.5 Taille des registres internes :

Le micro-proc traite une information de 8 bits, 16 bits, 32 bits, 64 bits, en une fois, c’est l’unité de

mesure de l’information traitée (pendant une addition par ex.).

sur 8 bits, on manipule une donnée qui peut aller de à

sur 16 bits, on manipule une donnée qui peut aller de à

sur 32 bits, on manipule une donnée qui peut aller de à

sur 64 bits, on manipule une donnée qui peut aller de à

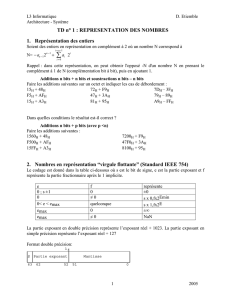

1.6 Taille du bus de données

Généralement de la même taille que les registres internes, mais ...

processeur

Reg. internes

Reg. externes

386 SX

32 bits

16 bits

386 DX

32 bits

32 bits

Pentium4, Athlon

32 bits

64 bits

Digital 21264

64 bits

128 bits

Athlon 64,

Opteron

64 bits

128 bits

1.7 Taille du bus d’adresses

i8088 et i8086 : 20 bits d’adresse, donc capacité d’adressage : ...........

i80286 :24 bits d’adresse, donc capacité d’adressage : .........

i80386DX :32 bits d’adresse, donc capacité d’adressage : .........

Pentium : bits d’adresse, donc capacité d’adressage : .........

Pentium pro : bits d’adresse, donc capacité d’adressage : .........

Pentium 4 : bits d’adresse, donc capacité d’adressage : .........

Athlon 64 : bits d’adresse, donc une capacité d’adressage : ……..

Le fait de stocker les adresses mémoire en 64 bits permet de dépasser la limite de 4 Go liée au codage

binaire sur 32 bits pour la passer à 256 Teraoctet du fait d’une "limitation" à 48 bits du codage de la

mémoire virtuelle. On notera toutefois qu’Intel a de son côté pu outrepasser cette limite de 4 Go sur ces

Xeon pour atteindre 64 Go, même si ce mode à des limitations. Là encore, ceci ne sera pas vraiment

utile pour le commun des mortels.( http://www.hardware.fr)

1.8 La fréquence d’horloge

Le HERTZ :

P.GRANDADAM BTS INFORMATIQUE DE GESTION page 3

Lyc Bonaparte Toulon TECHNOLOGIE DES COMPOSANTS D’UN ORDINATEUR poly nov 2007

Evolution de la fréquence d’horloge des processeurs :

30000

0

20000

0

10000

0

900

800

700

600

500

400

300

200

100

0

1980 1985 1990 1995 2000 2005 2010

1.9 Le Co-Processeur Arithmétique

1.10 Le multiplicateur de fréquence

Fréquence des cartes mères : 66, 75, 100, 133 MHz …

http://www.tomshardware.fr/processeur_le_core_2_duo_plus_fort_que_l_athlon_64_x2_-art-1315-2.html

P.GRANDADAM BTS INFORMATIQUE DE GESTION page 4

Lyc Bonaparte Toulon TECHNOLOGIE DES COMPOSANTS D’UN ORDINATEUR poly nov 2007

1.11 Interactions entre Volt, MHz, Watt, Intégration puce

Pour augmenter la puissance du processeur, il faut augmenter

………….. Mais ………

………….. Mais ………..

On peut mettre un …………. Mais çà fait du bruit !!!

Pour diminuer le TDP : T D P , il faut :

……………

…………….

On peut aussi optimiser l'architecture du processeur :

http://www.tomshardware.fr

1.12 Jeu d’instructions

X86

MMX

3Dnow!

SSE

AMD64

EMT64T

1.13 Processeur CISC

1.14 Processeur RISC

P.GRANDADAM BTS INFORMATIQUE DE GESTION page 5

Lyc Bonaparte Toulon TECHNOLOGIE DES COMPOSANTS D’UN ORDINATEUR poly nov 2007

1.15 L’architecture PIPE LINE

Introduite sur le 486

Pour exécuter une instruction processeur (recup une inst assembleur i++;)

Il faut enchaîner l'exécution de plusieurs micro-instructions :

Lecture de l'instruction (prefetch)

Décodage du code opération et des conditions d'adressage (decode)

Génération d'adresse pour récupérer l'opérande (adress generate)

Exécuter l'opération (exec)

Stockage du résultat en mémoire (write back)

Ces 5 opérations sont à exécuter de manière séquentielle !

Si on a plusieurs instructions de ce genre qui se suivent, on peut faire du travail à la chaîne :

Cycle m

Cycle m+1

Cycle m+2

Cycle m+3

Cycle m+4

Cycle m+5

Cycle m+6

Cycle m+7

Cycle m+8

Instr n° n

prefetch

decode

ad.generate

exec

write back

Instr n° n+1

prefetch

decode

ad.generate

exec

write back

Instr n° n+2

prefetch

decode

ad.generate

exec

write back

Instr n° n+3

prefetch

decode

ad.generate

exec

write back

Instr n° n+4

prefetch

decode

ad.generate

exec

Instr n° n+5

prefetch

decode

ad.generate

Instr n° n+6

prefetch

decode

Instr n° n+7

prefetch

Contraintes :

1.16 SUPERSCALAIRE

1.17 PREDICTION DE BRANCHEMENT, exécution spéculative

1.18 SISD :

Single Instruction Single Data : Une instruction traite une donnée. Traitement des données par le

processeur : 3 étapes se succèdent :

chargement de la donnée de la mémoire dans le processeur, traitement et rangement du résultat

en mémoire.

1.19 SIMD :

Single Instruction Multiple Data : Une seule instruction est utilisée pour effectuer le même traitement

sur plusieurs données fréquent avec MMX et SSE.

1.20 MIMD :

Multiple Instruction Multiple Data : Machines parallèles : IA, process …

Cluster VMS-Digital , MS-NT-clustering

1 processeur + mémoire locale (mémoire répartie), n fois + mémoire partagée pour communication entre

processeurs

1.21 EPIC : EXPLICIT PARALLEL INSTRUCTION COMPUTING

6

6

7

7

1

/

7

100%