Circuits Intégrés Analogiques

Circuits Intégrés Analogiques

ERII 4 – Mars 2011

Soin de la copie noté. Notes personnelles autorisées. Durée : 1h30

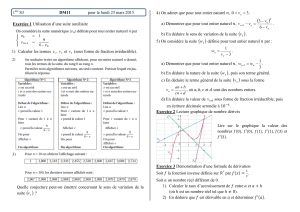

On souhaite étudier les performances de l’amplificateur ci-contre.

La technologie utilisée a les caractéristiques suivantes :

• MOS à canal P : µp.Cox = 50 µA/V2 ; Vtp = -0,7 V ; λp = 0,012 V-1

• MOS à canal N : µn.Cox = 125 µA/V2 ; Vtn = 0,5 V ; λn = 0,008 V-1

On négligera les effets de polarisation du substrat. On prendra Vdd = +3.3V.

A) Polarisation et performances élémentaires (7 points).

On considère que le générateur de courant est idéal.

1°) Dimensionner T3 et T4 de façon à ce que Vout soit égal à 0.7V

2°) Donner le schéma petit-signal de l’étage et en déduire l’expression du gain

différentiel en fonction de gm2, gds2 et gds4.

3°) En déduire le rapport de dimensions de T1 et T2 de façon à ce que ce gain soit de 1000.

4°) On connecte sur la sortie de l’étage une capacité CL. Donner la nouvelle expression du gain

AvBF(p) en fonction de gm2, gds2, gds4 et gL=CLp. En déduire la valeur de capacité nécessaire pour avoir

une fréquence de coupure de 160Hz. Quel est alors la fréquence de gain unitaire de cet étage ?

B) Etude du bruit ramené en entrée (4 points).

1°) Donner une expression de la densité de puissance de bruit en sortie vno

2 en fonction du bruit

d’entrée des transistors, de leur transconductance et de la résistance de sortie du montage. En déduire

la densité de puissance de bruit ramené en entrée.

2°) En ne prenant en compte que le bruit thermique, donner l’expression de ce bruit en fonction des

transconductances des transistors. En déduire les conditions sur les Veff des transistors permettant de

minimiser le bruit ramené en entrée.

Note : on rappelle que la densité de puissance de bruit thermique en entrée d’un transistor est donnée par

l’expression suivante :

= 4

.

C) Etude de l’offset d’entrée (4 points).

1°) En supposant que le signal d’entrée est nul, calculer la variation de tension de sortie due à

l’incertitude sur le courant de saturation du transistor T2. Faites de même pour le transistor T4.

2°) En déduire une expression de l’offset d’entrée maximum de cet étage.

3°) En déduire les conditions permettant de minimiser cet offset.

Note : on rappelle que l’incertitude sur le courant de saturation est donnée par l’expression ci-dessous :

D) Etude du taux de réjection de mode commun (5 points).

On prendra maintenant en compte la résistance de sortie Rb de la source de courant.

1°) On relie les deux entrées de l’étage, établir la relation entre une petite variation de la tension de

mode commun vmc et la variation du courant délivré par la source de courant ib en supposant que le Veff

des transistors n’est pas affecté.

2°) Dessiner, en faisant cette hypothèse, le schéma petit-signal permettant d’étudier le gain de mode

commun Amc=vout/vmc.

3°) Donner l’expression précise du courant i4 traversant la résistance de sortie du transistor M4 puis

calculer Amc et le taux de réjection de mode commun CMRR=Av/Amc.

Note : le gain de mode commun étant faible, il faudra prendre garde de ne pas utiliser les

simplifications habituelles.

LW

LW

µC

µC

V

V

I

I

ox

ox

eff

t

dsat

dsat

/

/

.2 ∆

+

∆

+

∆

=

∆

M4

Vdd

M1

M3

M2

Vin+ Vin-

Vout

Ib=10µA

1

/

1

100%