Chapitre IV

TEC586 Microcalculateurs

Chapitre IV Conception d’un processeur de base

Option contrôle

1

Chapitre IV

C

Co

on

nc

ce

ep

pt

ti

io

on

n

d

d’

’u

un

n

p

pr

ro

oc

ce

es

ss

se

eu

ur

r

d

de

e

b

ba

as

se

e

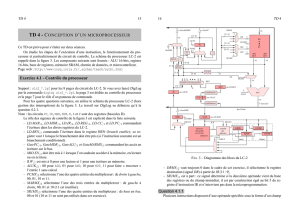

I Introduction :

Les éléments vus dans les chapitres I , II, et III seront utilisés dans ce chapitre, afin de

concevoir un processeur de base, possédant une structure simple, mais complète.

Un processeur classique est principalement réalisé à partir de circuits logiques ; le chapitre I

nous a permis de revoir, et recenser les circuits combinatoires, et séquentiels de base

essentiels pour la réalisation de tout circuit logique.

Dans un processeur, ou unité centrale de traitement, les informations stockées dans les

registres sont traitées, et subissent des opérations arithmétiques, logiques, de transfert, ou de

décalage ; le langage de transfert inter registres a été défini, et il a été montré comment les

circuits réalisant ces différentes opérations, sont décrits par le langage symbolique LTR.

Le chapitre III a montré différentes organisations classiques de processeurs à usage général

concernant les structures de bus, les modes d’adressage, l’organisation des registres, les

répertoires d’instructions…

Dans ce chapitre des choix , des hypothèses préliminaires seront faits concernant

l’organisation, le répertoire d’instructions et la puissance du processeur à concevoir.

Le langage de transfert inter registres, décrira les circuits des opérations qui seront exécutées à

chaque impulsion d’horloge , pour chaque instruction. Les différents modules constituant le

processeur de base seront construits pour être ensuite assemblés pour former le processeur de

base.

Choix du type de

processeur

et Hypothèses

Description de ses micro

opérations en LTR

Construction du circuit

Chapitre 111

Chapitre 11

Chapitre 1

Choix d’une

organisation

Initiation au

langage de

transfert inter

registre LTR

Rappel des

principaux

circuits

Etapes de conception et de réalisation du Processeur de base

TEC586 Microcalculateurs

Chapitre IV Conception d’un processeur de base

Option contrôle

2

II Les hypothèses

Le processeur de base étant un processeur didactique, il ne sera pas nécessaire de le doter de

puissance, vu que cela compliquerait ses circuits (on peut noter cependant, qu’un processeur

puissant tel que le Pentium, ou le Power PC, est constitué d’unités relativement simples

fonctionnant en parallèle ; le principe adopté pour la conception du processeur de base reste

donc valable et sera accompagné d’outils de CAO de plus en plus disponibles et modernes).

Les hypothèses suivantes seront donc émises

1. L’organisation des registres : on choisira la plus simple, soit l’organisation à

Accumulateur.

2. La mémoire centrale : sera de 4Kx16

3. Organisation de bus :

Le registre MAR sera utilisé pour gérer le bus d’adresse de la mémoire

Le registre MDR sera utilisé pour gérer le bus de données de la mémoire

Le bus d’Entrée/Sorties : sera géré en entrée par le registre d’entrées INPR et

en sortie par le registre de sortie OUTR et sera de 8 bits.

4. Les modes d’adressage : on en choisit 2 : le mode Direct et le mode indirect

(Remarque : un troisième mode, immédiat, sera introduit plus tard, car, bien que

nécessaire, il ne respecte pas certaines des hypothèses émises dans ce paragraphe).

5. Une instruction occupe un seul mot, ou case mémoire.

6. Un répertoire d’instructions : réduit mais complet, permettra d’exécuter

n’importe quelle tâche, moyennant le programme adéquat ; il sera défini plus loin dans ce

chapitre, et sera composé d’instructions:

arithmétiques

logiques

de transfert

de décalage

d’entrées / Sorties

TEC586 Microcalculateurs

Chapitre IV Conception d’un processeur de base

Option contrôle

3

II Conséquences des Hypothèses

1. La taille des registres

Le processeur de base est constitué des éléments suivants :

Le processeur possède une organisation à accumulateur : donc l’UAL recevra à sa

première entrée, l’accumulateur, et à sa seconde entrée le MDR (chargé de la donnée lue

de la mémoire.

La RAM est de 4Kx16 : elle possède donc 4x1024 mots de 16 bits, soit 12 lignes

d’adresse, et 16 lignes de données. Ainsi tous les registres d’adresse (PC, MAR) seront à

12 bits, et tous les registres de données, seront à 16 bits.

Une instruction est dans un seul mot de la mémoire qui est de 16 bits : le registre

d’instructions RI est sur 16 bits.

Le bus d’E/S est de 8 bits : les registres INPR et OUTR sont donc sur 8 bits

Unité

De

contrôle

AC

MDR

1 16

1 16

RI

1 16

MAR

1 12

PC

1 12

OUTR

1 8

INPR

1 8

Unité centrale

Périphériques

Mémoire

centrale

Principaux éléments du processeur de base

TEC586 Microcalculateurs

Chapitre IV Conception d’un processeur de base

Option contrôle

4

2. Le format des instructions

Le processeur ayant une organisation à AC, possède alors, une seule zone d’adresse comme le

montre la figure ci-dessous :.

M : est sur un seul bit puisqu’on a 2 modes d’adressage ; on l’appellera I pour le

processeur de base.

La mémoire étant de 4Kx16, les adresses sont de 12 bits, et donc la zone d’adresse

occupera 12 bits.

Le code OP occupera les bits restants, soit 3 bits

Problème : On peut à première vue définir uniquement 23 = 8 instructions, ce qui ne

permettra pas la création d’un répertoire d’instructions complet

Solution : On utilise le fait qu’on puisse classer les instructions selon trois types :

Type 1 : Instructions à référence mémoire ou IRM : ces instructions ont besoin d’un

opérande en mémoire, et doivent donc indiquer son adresse, et le mode d’adressage à

utiliser. Les 16 bits de l’instruction sont utilisés.

Exemple : ADD M(x) ; AC<- (AC)+ M(x) où x est l’adresse de l’opérande

Type 2 : Instructions à référence registre ou IRR : ces instruction n’ont besoin que

des informations stockées dans les registres de l’unité centrale. Elles n’ont pas besoin de

spécifier d’adresse ni de mode d’adressage. Les bits de la zone d’adresse, et du mode

d’adressage peuvent avoir une autre fonction.

Exemple : CLA ; AC <- 0

Type 3 : les instructions d’entrée/sortie ou IES : Ces instructions n’ont pas besoin de

spécifier d’adresse ni de mode d’adressage, puisqu’elles permettent de s’adresser en

entrée ou en sortie aux périphériques.

Exemple : IN portA ; AC <- donnée provenant d’un périphérique par le port A

On remarque donc que l’adresse et le bit de mode ne sont pas demandés par toutes les

instructions. Cette propriété sera utilisée ci-dessous pour codifier les instructions.

M

OP

ADR

1

12

TEC586 Microcalculateurs

Chapitre IV Conception d’un processeur de base

Option contrôle

5

IV Distinction et codification des IRM, IRR, et IES

1. Distinction des IRM, IRR, IES

C’est le code OP qui doit permettre à l’unité de contrôle de reconnaître une instruction de

façon unique.

On utilise une des 8 combinaisons du code OP, 111 par exemple, pour différencier les IRM

des autres instructions : Si OP = 111 alors l’instruction n’est pas une IRM .

Si OP ≠ 111 : l’instruction est une IRM, et les 16 bits de l’instruction sont utilisés, I

pour le mode d’adressage, OP 3 bits pour définir une instruction IRM, et les 12 bits

restants spécifient l’adresse à utiliser.

Si OP = 111 : l’instruction n’est pas une IRM ; elle est soit de type IRR soit IES ;

puisque le bit de mode I est libre on l’utilise pour différencier les 2 types

Si I = 0 c’est une IRR : et les 12 bits de la zone d’adresse sont utilisés pour

déterminer laquelle. On voit qu’il est possible de définir 212 instructions différentes, on

se contentera d’en définir 12.

Si I= 1 c’est une IES : et les 12 bits de la zone d’adresse sont utilisés pour

déterminer laquelle. On voit qu’il est possible de définir 212 instructions différentes ,

on se contentera d’en définir 4.

OP=111

I=1

IE/S

IRR

IRM

N

N

O

O

Distinction entre les IRM, IRR, et IES

1

111

OP IES

I

OP≠111

ADR

0

111

OP IRR

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

1

/

35

100%