Utilisation des composants Deep Sub

19e Congrès de Maîtrise des Risques et Sûreté de Fonctionnement - Dijon 21-23 octobre 2014

UTILISATION DES COMPOSANTS DEEP SUB-MICRON DANS LE CONTEXTE

AERONAUTIQUE

DEEP SUB-MICRON COMPONENTS IN THE AEROSPACE CONTEXT

Julie Berthon et Didier Regis Guillaume Hubert

Thales Avionics ONERA

Rue Toussaint Catros 2 avenue Edouard Belin

33185 Le Haillan 31055 Toulouse

(+33)5 56 13 44 90 +(33)5 62 25 28 85

[email protected]sgroup.com

(+33)5 57 26 77 21

Résumé

Depuis plus de 40 ans, la loi expérimentale de Gordon Moore prédit la progression du niveau d’intégration des composants

électroniques numériques et oriente par là même les développements électroniques.

Jusqu'à ces dernières années, cette évolution n’a pas eu de contrepartie mesurable sur la qualité des composants ; mais ceci

commence à n’être plus tout à fait vrai.

Cet article adresse l’impact de la réduction de la finesse de gravure des composants électroniques numériques sur leur fiabilité,

et ses répercussions dans les analyses de sécurité des systèmes aéronautiques embarqués. Dans ce cadre, il analyse d’un

point de vue qualitatif et quantitatif le comportement des technologies Deep Sub-Micron en termes de robustesse et de fiabilité

et adresse plus particulièrement trois fondamentaux des analyses de sécurité des systèmes aéronautiques : le taux de

défaillance, la durée de vie et la sensibilité aux radiations atmosphériques.

Summary

For more than 40 years, Gordon Moore’s experimental law has been predicting the evolution of the number of transistors in

integrated circuits, thereby guiding electronics developments.

Until last years, this evolution did not have any measurable impact on components’ quality; but the trend is beginning to reverse.

This paper is addressing the impact of scaling on the reliability of integrated circuits. It is analyzing - from both qualitative and

quantitative point of view - the behavior of Deep Sub-Micron technologies in terms of robustness and reliability. It is particularly

focusing on three basics of safety analyses for aeronautical systems: failure rates, lifetimes and atmospheric radiations’

susceptibility.

Introduction

L’acronyme anglais DSM (Deep Sub-Micron) fait référence aux composants « nettement sub-microniques » c’est-à-dire dont la

finesse de gravure est très inférieure au micron. Si ces composants sont apparus il y a quelques années déjà et sont utilisés

dans les applications aéronautiques depuis plus de 10 ans, la course à la miniaturisation s’est accélérée ces dernières années :

de 90nm en 2004, le nœud technologique - tel que défini par l’ITRS1 - est tombé à 28 nm en 2012 et devrait passer sous les 10

nm à l’horizon 2020.

Cette miniaturisation a deux motivations principales : d’une part, un objectif permanent de réduction des coûts et, d’autre part,

un impérieux besoin d'augmenter les puissances de calcul et de stockage de l'information, chose qui ne peut se faire qu'en

intégrant plus de transistors sur une même puce.

Si un tel niveau d’intégration offre des performances inégalées et suscite un grand intérêt pour les applications embarquées,

des études récentes montrent qu’il pose un certain nombre de problèmes en termes de robustesse2 et de fiabilité, parmi

lesquels :

• L’apparition de défaillances de jeunesse difficiles à piéger en déverminage ;

• Des problèmes d’intégrité de signal liés à des sources de bruits externes ou internes au composant ;

• Une vulnérabilité accrue aux particules de haute énergie ;

• La dégradation du WCET3 ;

• L’impact prématuré de mécanismes de dégradation entraînant une forte réduction de la durée de vie.

La possible remise en cause de la notion de taux de défaillance constant, la réduction de la durée de vie et la

vulnérabilité accrue aux particules de haute énergie sont les problématiques les plus critiques en termes de sûreté de

fonctionnement.

Ces problématiques sont très dépendantes de la technologie mais également étroitement liées aux contraintes

environnementales et aux conditions d’utilisation des composants : tension d’alimentation, fréquence de fonctionnement, etc.

1 L’ITRS (International Technology Roadmap for Semiconductors) est une organisation résultant d’un consortium d'acteurs de la

micro-électronique, sponsorisée par les associations nationales de l'industrie des semi-conducteurs européennes, américaines

et asiatiques. Son principal objectif est la rédaction d’une « feuille de route » identifiant les barrières techniques à franchir pour

chaque nouvelle génération de composant et servant de référence aux industriels de la microélectronique.

2 Selon l’IEEE, degré selon lequel un système, ou un composant, peut fonctionner correctement en présence d’entrée invalides

ou de conditions environnementales stressantes.

3 Le « Worst Case Execution Time » est défini comme le temps maximal nécessaire à l’exécution d’une instruction.

Communication 1C-4 Page 1 sur 10

19e Congrès de Maîtrise des Risques et Sûreté de Fonctionnement - Dijon 21-23 octobre 2014

Malheureusement pour les concepteurs aéronautiques, les marges de manœuvre sont faibles. Les composants électroniques

ne sont ni conçus, ni testés, ni même mesurés pour adresser leurs besoins. Le marché du composant est dominé par

l’électronique grand public pour laquelle la fiabilité n’est pas une contrainte forte, et dont les exigences sont incompatibles de

celles auxquelles sont soumis les matériels sécuritaires : quand l’électronique grand public requiert des taux de défaillance de

l’ordre de 1000 FIT 4 et des durées de vie comprises entre 1 et 5 ans, le secteur aéronautique requiert des taux de défaillance

inférieurs à 100 FIT et des durées de vie comprises entre 10 et 30 ans.

Ces problématiques sont accentuées par l’introduction dans les composants de nouveaux matériaux qui, s’ils permettent

d’atteindre les objectifs de performance exigés par le marché, introduisent une incertitude quant à leur tenue dans le temps.

Le domaine aéronautique doit donc relever un défi de taille : utiliser des technologies nécessaires à ses besoins en puissance

de calcul et capacité de stockage mais incompatibles de ses exigences de fiabilité, et chercher des solutions permettant

d’utiliser des composants dans des conditions et des environnements pour lesquels ils ne sont ni spécifiés ni garantis.

1. Mécanismes de défaillance des composants DSM

1.1. Mécanismes de défaillance des circuits intégrés

Soulignons tout d’abord que le terme circuit intégré désigne ici le circuit électronique (que nous appelons plus communément

puce électronique) et non le composant assemblé. Les mécanismes de dégradation abordés dans ce paragraphe sont donc

propres au circuit intégré, et non au boîtier ou aux connections boîtier - circuit imprimé.

Les mécanismes de dégradation des circuits intégrés sont largement documentés et cette communication les adresse dans le

seul objectif d’améliorer la compréhension de la problématique générale.

Il est d’usage de distinguer les mécanismes agissant au niveau des connections intra silicium (BEOL5) et les mécanismes

agissant au niveau des transistors (FEOL6).

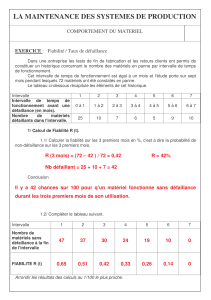

Les zones BEOL et FEOL sont représentés sur la Figure 1 tandis que les différents mécanismes sont localisés sur la Figure 2.

Trois principaux mécanismes de dégradation agissent au niveau des connections intra silicium.

Electromigration, EM

L’électromigration est un mécanisme d’usure lié à la migration d’atomes dans un conducteur métallique. Cette migration peut

avoir deux effets :

• La formation de trous au niveau de la cathode, entraînant une augmentation de la résistance et pouvant aller jusqu’à

l’ouverture d’une ligne ;

• L’accumulation de matière au niveau de l’anode, entraînant un court-circuit entre deux lignes.

Stress Migration, SM

Ce mécanisme de dégradation se manifeste généralement par une fissuration des couches constituant la puce, fissuration

induite par des contraintes mécaniques dues à la différence de coefficients de dilatation thermique entre les différentes

couches.

Time Dependent Dielectric Breakdown in Inter-Layer Dielectric, TDDB in ILD

La rupture d’oxyde intermétallique est une rupture de l’oxyde entre deux niveaux de métallisation. Le diélectrique qui, à certains

endroits, est pris entre deux niveaux de métallisation, crée une capacité et est confronté à une accumulation temporelle de

charges électriques aux interfaces des métallisations ; ces charges sont à l’origine de courants de fuite pouvant entraîner une

rupture de l’oxyde lorsqu’un chemin de conduction se forme entre la cathode et l’anode de la capacité ainsi crée.

Trois principaux mécanismes de dégradation agissent au niveau des transistors.

Time Dependent Dielectric Breakdown in Gate Oxide, TDDB in GO

La rupture d’oxyde de grille est une rupture de la couche d’oxyde située au niveau de la grille du transistor. Elle est liée à une

accumulation temporelle de charges électriques aux interfaces oxyde-silicium, charges à l’origine de courants de fuite pouvant

entraîner une rupture de l’oxyde de grille lorsqu’un chemin de conduction se forme entre substrat (cathode) et grille (anode).

Hot Carrier Injection, HCI

4 FIT ou Failure In Time, taux de défaillance exprimé en 10-9 défaillance par heure

5 Le Back End Of Line désigne la zone dans laquelle sont empilées les différentes couches de métal et réalisées les différentes

interconnections entre transistors

6 Le Front End Of Line désigne la zone active du composant, celle ou sont arrangés les transistors

EM

TDDB

TDDB

NBTI

HCI

SM

Figure 2. Les différents mécanismes de défaillance du

circuit intégré

Figure 1. Zone BEOL et zone FEOL dans un

circuit intégré

Communication 1C-4 Page 2 sur 10

19e Congrès de Maîtrise des Risques et Sûreté de Fonctionnement - Dijon 21-23 octobre 2014

L’injection de porteurs chauds est un mécanisme d’usure se produisant lorsque les électrons traversant le canal acquièrent

suffisamment d’énergie pour être injectés dans l’oxyde. Ce phénomène entraîne une dégradation des paramètres électriques du

transistor, parmi lesquels une augmentation de la tension de seuil et donc des temps de commutation.

(Negative or Positive) Bias Temperature Instability, (N or P) BTI

L’instabilité de tension de seuil en température est un mécanisme d’usure du transistor MOS apparaissant à haute température

lorsque le transistor MOS est polarisé en mode inversion.

Les mécanismes présentés dans ce paragraphe sont des mécanismes de vieillissement.

Si la rupture d’oxyde de grille peut se manifester par une défaillance catalectique - lorsqu’un stress suffisamment important

conduit à une rupture franche - et si la rupture d’oxyde intermétallique et l’électromigration peuvent causer des défaillances

aléatoires, ces mécanismes seront le plus souvent à l’origine de défaillances dites d’usure.

1.2. Impact de la miniaturisation

Il n’y a pas vraiment de mécanisme de défaillance propre aux circuits intégrés DSM mais plutôt une aggravation et/ou une

occurrence prématurée des mécanismes de défaillance décrits au paragraphe précédent.

En effet, l’intégration et la miniaturisation ont des impacts forts sur l’architecture et la géométrie des circuits mais également sur

leur comportement électrique.

Tout d’abord, l’augmentation du nombre de transistors est à l’origine d’une superposition des niveaux d’interconnections

métalliques - et donc d’une augmentation de la densité de métallisation - favorisant les mécanismes d’électromigration, de

Stress Migration et la rupture d’oxyde intermétallique.

De manière plus générale, la miniaturisation impose une réduction des géométries élémentaires qui favorise l’ensemble des

mécanismes de défaillance.

De plus, la réduction des motifs géométriques (et tout particulièrement de l’épaisseur d’oxyde de grille) et la réduction de la

tension de polarisation n’évoluent pas dans les mêmes proportions ; il en résulte une augmentation des champs électriques

impactant les mécanismes de défaillance sensibles au stress électrique :

• L’augmentation de la densité de courant dans les interconnections métalliques favorise l’électromigration ;

• L’augmentation du champ électrique au niveau des interconnections métalliques et de la grille favorise la rupture

d’oxyde intermétallique et la rupture d’oxyde de grille ;

• L’augmentation du champ électrique dans le canal favorise globalement les mécanismes HCI et NBTI.

Par ailleurs, presque7 tous ces mécanismes de défaillances sont naturellement accélérés par les hautes températures. Or,

l’augmentation du nombre de transistors entraîne une augmentation de la puissance dissipée et, par auto-échauffement, de la

température …

Le tableau 1 résume les différents mécanismes de dégradation, les éléments des DSM favorisant ces mécanismes ainsi que les

stresses susceptibles de les accélérer.

Tableau 1

Mécanisme de

dégradation

Localisation

Impact de la miniaturisation

Stresses accélérant le mécanisme

BEOL FEOL

Stress

électrique

Température

haute

Température

basse

EM X

Augmentation de la densité de

métallisation

Diminution de la largeur et de

l’épaisseur des lignes de métal

Augmentation de la d

ensité de

courant dans les interconnections

X X

SM X

Augmentation de la densité de

métallisation

Diminution de la largeur et de

l’épaisseur des lignes de métal

X

TDDB ILD X

Diminution de l’épaisseur d’oxyde

Augmentation du champ électrique

X X

TDDB GO X

Diminution de l’épaisseur d’oxyde

Augmentation du champ électrique

X X

HCI X

Diminution de la longueur et de

l’épaisseur du drain

Diminution de l’épaisseur d’oxyde

Augmentation du champ électrique

X X

NBTI X

Diminution de l’épaisseur d’oxyde

Augmentation du champ électrique

X X

7 Seul le HCI est accéléré par les basses températures car les électrons sont plus mobiles et donc plus énergétiques à basse

température.

Communication 1C-4 Page 3 sur 10

19e Congrès de Maîtrise des Risques et Sûreté de Fonctionnement - Dijon 21-23 octobre 2014

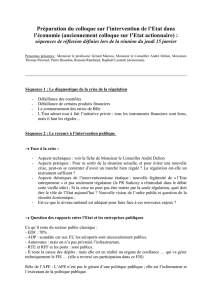

2. Vers une remise en question de la traditionnelle courbe en baignoire ?

2.1. La courbe en baignoire

Rappelons tout d’abord, sans trop insister sur ce phénomène connu des fiabilistes, que le taux de défaillance d’un composant

électronique en fonction de l’âge évolue généralement en trois phases :

• La période de jeunesse - ou de mortalité infantile - caractérisée par un taux de défaillance relativement élevé mais

décroissant, dû à la manifestation de défauts de jeunesse ;

• La période de vie utile caractérisée par un taux de défaillance constant et faible, dû à la manifestation de défaillances

aléatoires ;

• La période de vieillissement - ou d’usure - caractérisée par un taux de défaillance croissant et dû à la manifestation

de phénomènes de dégradation.

Ces trois phases sont communément illustrées sur une courbe caractéristique, dite « courbe en baignoire », telle que celle

représentée sur la Figure 3. A chacune d’elles est associée une distribution de Weibull dont le paramètre β caractérise la nature

des défaillances observées.

A ce stade de la discussion, il est intéressant de positionner sur cette courbe les différents types de défaillances auxquels

peuvent être sujets les composants DSM :

Période de jeunesse

Elle verra plutôt se manifester les défaillances liées :

• A la présence de défauts introduits durant la conception ou la production (incompatibilité thermomécanique entre

deux matériaux, présence de fissures, impuretés dans les couches d’interface, over/under-bonding, etc.) ;

• A l’utilisation de technologies ou de procédés de fabrication insuffisamment matures.

Période de vie utile

Elle verra se manifester :

• Des pannes accidentelles liées à des faiblesses de composants ;

• Des pannes catalectiques liées à des over-stresses (ESD, chocs thermiques, …) ;

• Quelques ruptures franches de l’oxyde de grille et quelques défaillances liées à l’électromigration ou à une rupture

d’oxyde intermétallique ;

• Des pannes liées à des SEU/MBU.

Période de vieillissement

Elle verra se manifester les défaillances d’usure liées aux différents mécanismes de dégradation évoqués dans le paragraphe 1

: EM, SM, TDDB, NTBI, HCI.

Figure 3. La courbe en baignoire, image d’Epinal de la fiabilité des composants électroniques

Les analyses de sécurité des systèmes électroniques sont généralement réalisées sous l’hypothèse d’un taux de défaillance

constant. Cette hypothèse est admissible - et généralement admise - considérant :

• Que la sélection de composants de qualité combinée à un déverminage approprié permet d’éliminer les pannes de

jeunesse,

• Que les matériels sont généralement rebutés avant que les composants n’entrent dans la phase d’usure c’est-à-dire

avant que le taux d’avarie lié au vieillissement ne devienne supérieur au taux d’avarie de la vie utile,

• Et qu’ainsi, les composants ne sont utilisés qu’à taux de défaillance à peu près constant.

Mais cette hypothèse, fondamentale dans la conduite des analyses de sécurité des systèmes aéronautiques, est remise en

question depuis les années 2000. De nombreuses publications (Mak, 2005) (Intel, 2002) (…) alertent alors sur le potentiel

impact de l’intégration sur la traditionnelle courbe en baignoire :

• Un allongement de la période de jeunesse ;

• Une augmentation du taux de défaillance aléatoire ;

• Une translation temporelle de la période de vieillissement.

Période de jeunesse

β<1

Période de vie utile

β=1

Période d’usure

β>1

Taux de défaillance

Défauts de conception

ou de production

EM, SM, TDDB, NBTI,

HCI

Over-stresses (ESD, T°C …)

SEU

TDDB GO & ILD, EM

Communication 1C-4 Page 4 sur 10

19e Congrès de Maîtrise des Risques et Sûreté de Fonctionnement - Dijon 21-23 octobre 2014

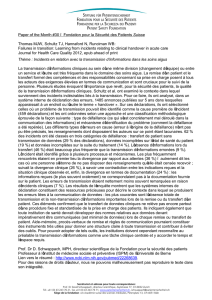

Temps

Rallongement de la période de jeunesse, augmentation du taux de

défaillances aléatoires et usure prématurée ?

Zone de validité des analyses

de sécurité

Taux de défaillance

180 nm et + :

DDV > 100 ans

30 nm et en-deçà :

DDV < 10 ans

Ainsi, la zone de validité des analyses de sécurité - conduites à taux de défaillance constant - se voit réduite à chaque nœud

technologique (Figure 4).

2.2. Des défaillances de jeunesse plus fréquentes et plus difficiles à piéger

Les composants DSM sont sujets à une augmentation des défaillances de jeunesse, augmentation qui est essentiellement liée

à trois causes :

• Tout d’abord, la complexité grandissante des circuits intégrés entraîne une augmentation du nombre de transistors et

du nombre de couches d’interconnections ;

• Ensuite, la réduction des géométries entraîne une variabilité de plus en plus en plus importante dans les procédés de

fabrication ;

• Enfin, la dimension des atomes étant invariante, l’intégration est de plus en plus portée par l’introduction de nouveaux

matériaux dans les assemblages et de nouveaux procédés de fabrication, moins bien maîtrisés et donc moins

matures ; à titre d’exemple, le passage sous les 20nm nécessite l’abandon de la technologie « planar » classique et

impose l’utilisation de technologies « FinFet8 » ou « FDSOI9 » dont on ne connait pas encore la robustesse et la

fiabilité.

Parallèlement, le déverminage voit son efficacité réduite de génération en génération. La principale raison est l’aggravation des

conditions de fonctionnement nominales des circuits intégrés et donc la réduction des facteurs d’accélération entre conditions

nominales et conditions de déverminage.

L’aggravation des conditions de fonctionnement nominales a deux explications :

• Tout d’abord, l’inhomogénéité de l’équation d’intégration : si la géométrie des transistors est fortement réduite à

chaque nœud technologique, les paramètres physiques et surtout électriques n’évoluent pas dans les mêmes

proportions et il s’ensuit une augmentation du champ électrique et une augmentation de la température de jonction

par effet Joule.

• Ensuite, l’introduction de mécanismes de régulation de la tension interne du circuit intégré complique l’application de

stresses accélérés en tension, réduisant l’efficacité du déverminage électrique.

Ainsi, l’efficacité du déverminage aurait diminué d’un facteur 10 entre le nœud technologique 180nm (Perdu, 2012) et le nœud

technologique 90nm, et cette tendance ne pourrait que s’accélérer.

2.3. Une augmentation du taux de défaillance aléatoire

Nous l’avons vu précédemment, les défaillances usuellement rencontrées dans la vie utile du composant sont essentiellement

liées à des surcharges accidentelles, à des ruptures franches de l’oxyde de grille (TDDB GO) ou à des évènements singuliers

(SEU/MBU) que nous traiterons dans un chapitre à part.

Globalement, l’augmentation du champ électrique et de la température de fonctionnement favorise le TDDB.

La diminution des tensions d’alimentation est, quant à elle, à l’origine d’une forte réduction de la marge de bruit qui devrait

descendre sous les 100mV à l’horizon 2015 (Binhong, 2011). Cette réduction de marge augmente la susceptibilité aux

interférences électromagnétiques dans le domaine fréquentiel et temporel.

8 FinFET est l'acronyme de Fin-Shaped Field Effect Transistor, Fin étant utilisé ici en rapport avec la forme que donne

l'architecture de ces transistors au drain et à la source, qui ressemblent alors à des ailerons.

9 Fully Depleted Silicon On Insulator

Figure 4. Vers une profonde remise en cause de la courbe en

baignoire

Communication 1C-4 Page 5 sur 10

6

6

7

7

8

8

9

9

10

10

1

/

10

100%