Module de CAO microélectronique « Conception d`un

Résumé— Cet article présente un module de CAO

microélectronique proposé dans le cadre de la formation de

5ème année en Génie Électrique à l'Institut National des

Sciences Appliquées de Strasbourg. Le contenu du cours

repose sur un projet de conception d'un circuit intégré mixte

devant remplir la fonction de « wattmètre ». Le module se

compose d'une partie théorique portant sur l'introduction au

langage de modélisation VHDL-AMS et la définition du cahier

des charges du projet, et d'une partie pratique de réalisation

du projet jusqu'au prototypage sur cible FPGA. Au delà du

cadre de l'initiation au langage de modélisation VHDL-AMS,

ce cours aborde des notions plus larges sur les méthodologies

de conception en microélectronique, le prototypage,

l'organisation et la gestion d'un projet et le travail d'équipe.

Mots clés— CAO microélectronique, modélisation, VHDL-

AMS, circuit intégré mixte, système sur puce, prototypage,

FPGA.

I.INTRODUCTION

E le pôle de MIcro et nanoélectronique du Grand-EST

(MIGREST) du CNFM propose un module de CAO

microélectronique aux étudiants en dernière année de

formation d'ingénieurs de l'Institut National des Sciences

Appliquées (INSA) de Strasbourg. Ce module s'inscrit dans

le cadre des projets de fin d'étude que doivent réaliser les

étudiants ayant choisi la spécialité Génie Électrique avec

option « Systèmes ».

L

La première partie de cet article présente le sujet du

projet. Les notions théoriques nécessaires à la réalisation de

ce projet, en l'occurrence le contenu du cours et

l'organisation des séances de cours et pratiques, sont

proposées dans la seconde partie. La troisième partie traite

de l'organisation du travail des étudiants, création de

groupes de travail, découpe hiérarchique, analyse du cahier

des charges. La dernière partie tente une analyse des

résultats avec quelques exemples de réalisation.

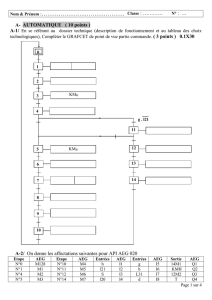

II.PRÉSENTATION DU SUJET DU PROJET

A.Contexte

Le sujet du projet, inspiré d'une problématique

industrielle réelle, porte sur la conception d'un « wattmètre »

intégré. Le principe de fonctionnement des compteurs

électriques conventionnels, utilisés par exemple pour la

tarification de la consommation électrique domestique,

repose sur l'utilisation de capteurs de courant et de tension

Manuscrit proposé aux Journées Pédagogiques de la Coordination

Nationale pour la Formation en Micro et nanoélectronique 2008.

associés à une électronique de conditionnement et

directement connectés à un microprocesseur. Ce dernier est

alors chargé d'effectuer tout à la fois la conversion

analogique-numérique et les opérations de calcul

(puissances actives et réactives, cos(ϕ), etc.). Une telle

structure montre très vite ses limites lorsqu'il s'agit de

produire à faible coût un compteur performant. Le corollaire

à ceci est un coût élevé lorsque des objectifs de

performances (précision et fonctionnalités) sont visés

puisque celles-ci sont conditionnées par l'utilisation d'un

processeur plus puissant (plus grande résolution du

convertisseur A/N, vitesse de calcul plus importante, etc.).

L'idée sous-jacente de ce projet consistait donc à

développer un circuit intégré en technologie CMOS

standard, et bas coût car produit en grand nombre, dédié au

pré-traitement des grandeurs électriques. Ce concept permet

d'augmenter les performances globales du compteur tout en

contenant les coûts du processeur puisque celui-ci peut

afficher des performances plus modestes, les données étant

pré-traitées en amont, et le cas échéant d'obtenir un produit

fini extrêmement versatile en terme de fonctionnalités. La

figure 1 montre la structure d'un tel compteur.

B.Structure du circuit intégré

Il s'agit d'un circuit de type ASIC (Application Specific

Integrated Circuit) mixte aux caractéristiques d'un système

sur puce. Son fonctionnement de base consiste dans un

premier temps à convertir en données numériques les

tensions provenant de deux capteurs placés sur un réseau

électrique monophasé. Ces capteurs ont pour rôle de fournir

des informations analogiques sur le courant et la tension de

ce réseau. Dans un second temps, les données numériques

servent à calculer la puissance sous une forme initialement

simplifiée (U∙I) puis à fournir le résultat également sous

forme numérique pour un traitement en aval par exemple au

moyen d'un DSP et/ou d'un microprocesseur. Des fonctions

annexes doivent permettre d'augmenter la souplesse

Module de CAO microélectronique

« Conception d’un wattmètre monophasé

intégré »

Fig. 1. Schéma bloc du compteur électrique.

Int égré

Couran t

Tension

Sorties réseaux num érique

Supervision

Réseau élect rique

V. Frick, Maître de conférences, Université Louis Pasteur – Strasbourg I

CNFM – Pôle MIGREST

MIGREST

P12

d'utilisation et de configuration du système. Une structure

générale de ce système est proposée dans la figure 2.

Fig. 2. Proposition de structure générale du « wattmètre » intégré.

III.CONTENU ET ORGANISATION DU COURS

A.Motivations et organisation

Étant donné le caractère mixte du circuit, l'introduction au

langage VHDL-AMS [1] est une approche idéale pour

permettre aux étudiants d'appréhender efficacement et

globalement ce projet. Il est clair que ce choix se fait au

détriment des techniques de conception spécifiques aux

structures analogiques pures (en l'occurrence le

dimensionnement des transistors à l'aide du modèle SPICE

LEVEL 1 [2]) qui requerrait un cours complet à elles seules.

Ce module de CAO, d'un volume total de 42 heures, se

décompose alors en deux parties, l'une théorique dans les

locaux de l'INSA, l'autre pratique dans les locaux du

MIGREST. Il est important de noter que 99% des étudiants

suivant ce module n'ont aucun bagage en VHDL-AMS et

plus largement en conception de circuits intégrés. Les pré-

requis sont donc d'ordre général en électronique et

traitement analogique et numérique du signal.

La partie théorique se déroule en séances communes

(cours magistral) représentant un volume horaire de

18 heures réparties en 9 séances de 2 heures.

La première séance est une introduction générale sur la

microélectronique, les microsystèmes, leurs technologies

actuelles et les méthodologies de conception. La

microélectronique étant une discipline particulière aux

matériels et outils de développement et de production lourds

et coûteux, l'occasion est saisie pour mettre l'accent sur les

enjeux économiques connexes. Une large partie (8 h) est

ensuite consacrée à l’introduction au langage VHDL-AMS

pour la modélisation, la simulation et la conception de

circuits intégrés à architectures mixtes

analogique/numérique. La dernière partie du cours (8 h) sert

d'illustration concrète des méthodologies précitées, par

l’établissement du cahier des charges détaillé du projet

« Wattmètre intégré monophasé » qui sera développé lors

des séances pratiques.

Il est important de souligner que l'organisation du cours

n'est pas linéaire d'un point de vue temporel. En effet, après

la séance introductive, les deux autres parties sont

imbriquées, par un jeu d'alternance entre l'une et l'autre. La

raison de ce choix est double, tant organisationnelle que

pédagogique.

D'un point de vue organisationnel, les séances pratiques

débutent avant la fin du cours. Afin que les étudiants

puissent progresser de manière constante dans leur projet il

est important qu'ils acquièrent simultanément la

connaissance du langage de modélisation et celle des

spécifications propres au circuit « wattmètre ». D'un point

de vue pédagogique, cette alternance permet de rompre avec

l'éventuelle monotonie du cours sur le langage VHDL-

AMS. En effet, l'apprentissage théorique d'un langage de

description matériel peut s'avérer fastidieux et le fait d'y

insérer régulièrement des extraits du projet à titre d'exemple

contribue fortement à accroître l'intérêt des étudiants pour la

matière. Leur implication en est d'autant plus forte.

Dans le support de cours remis aux étudiants dès la

première séance, les trois volets (introduction, VHDL-AMS

et Cahier des charges) sont toutefois, et pour des raisons de

clarté, parfaitement distincts.

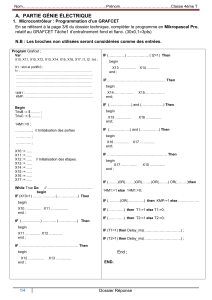

B.Initiation à la modélisation de systèmes mixtes : le

langage VHDL-AMS

Cette phase a pour but d'apporter aux étudiants les

connaissances suffisantes de ce langage pour leur permettre

de développer le projet en autonomie. Elle commence par

une présentation de la structure générale d'une entité de

conception. L’emphase est mise sur les distinctions entre les

langages de programmation logiciel et les langages de

description matériel.

Il est fondamental, déjà à ce stade, de faire prendre

conscience aux étudiants que chaque ligne de code a un

effet déterminant sur l'architecture électronique du circuit

qui en découlera. Cette notion est illustrée par l'analyse de

cas critiques tels que celui proposé dans la figure 3.

a.

!"#$

%&'(

)*+"+

,%&'(

-.*#/

/

,%&'(

-.*+0+/

/

/

!"/

b.

!1#$

%&'(

)*+0+

,%&'(

-.*202/

/

,%&'(

-.*#/

/

/

!1/

Fig. 3. Exemple d'analyse de cas critiques : a. Code et résultat de synthèse

sous Quartus II® d’une architecture mettant la priorité sur le front-montant

d'un signal d’horloge CLK. b. Code et résultat de synthèse sous Quartus II®

d’une architecture mettant la priorité sur le front descendant d'un signal

d'horloge CLK.

Étant donné le caractère mixte du VHDL-AMS la notion

de codes « synthétisables » et « non-synhétisables » est

abordée concomitamment à celle de hiérarchisation d'un

circuit, et par voie de conséquence du projet et de tout le

travail qui en découlera.

Le cours se poursuit par la présentation du langage dans

ses détails et particularités : les objets et leur « typage »

spécifique au langage de description matériel, les

affectations, les notions d'instructions concurrentes et

séquentielles (processus, procédures, etc.), les attributs.

Chaque notion est émaillée d'exemples de codage

MIGREST

P12

l'illustrant de manière générale ou, dans la mesure du

possible, en lien direct avec le projet.

C.Cahier des charges du projet

Lors des 8 heures de cours qui y sont dédiées, les

étudiants sont amenés à reconstituer le cahier des charges

des blocs qui constitueront le circuit, à partir des

spécifications sommaires regroupées dans le tableau 1.

Caractéristiques des signaux

d'entrée Valeur

34

0567%859":07(

$8; :0<=

06><=

Performances recherchées Valeur

88 0?0:@!+8

8A:0<=

."A6567

Tableau 1. Spécifications sommaires du circuit « wattmètre intégré ».

Une séance de travail collectif est consacrée à la lecture

commentée et à l'analyse des spécifications du circuit. La

réflexion est menée en table ronde par les étudiants eux-

mêmes, de telle sorte qu'ils s'approprient le sujet. La

structure de la figure 2 est un exemple de solution proposé

mais reste ouverte à toute discussion, ce qui offre donc

quelques degrés de liberté.

La proposition de la figure 2 découle des conjectures

suivantes :

–Le système étant mixte (entrées analogiques, sorties

numériques) il est donc indispensable d'opérer une

Conversion Analogique/Numérique (CAN). La

dynamique d'entrée et la précision souhaitée

permettent alors de statuer sur le format binaire. Une

résolution de 12 bits est a priori suffisante pour

satisfaire cette condition.

–La cadence de conversion est imposée par la bande

passante du signal d'entrée. Pour respecter le critère

de Shannon, celle-ci doit être supérieure ou égale à

6 kHz.

–Le choix de l'architecture du CAN dépend des

performances visées (cadence et résolution). Le CAN

proposée est de type modulateur Sigma-Delta (Σ∆)

du second ordre associé à un filtre à Réponse

Impulsionnelle Finie (RIF). Le choix du modulateur

est imposé pour des raisons de performance mais

également pour des raisons pratiques puisqu'il s'agit

du seul bloc qui ne soit pas « synthétisable ». Quant

aux autres blocs, ils doivent impérativement se prêter

à l’implantation sur cible FPGA. Ce point est discuté

plus en détail dans la section IV traitant de la

réalisation pratique.

–Le fait d'opter pour un convertisseur à sur-

échantillonnage implique l'intégration d'une fonction

de contrôle et de synchronisation de l'ensemble des

organes du circuit, en l'occurrence un séquenceur.

Les caractéristiques du RIF et le facteur de

décimation sont également imposés par le

modulateur.

–La fonction de wattmètre requiert un produit entre la

donnée « courant » et la donnée « tension ». Cela

conditionne le format de 24 bits en sortie du circuit.

Une fois les blocs identifiés, le cours se poursuit par

l'établissement détaillé de leurs spécifications internes. Il

s'agit essentiellement de développer les méthodologies de

description comportementale et d'apporter des éléments de

modélisation propres à chaque bloc.

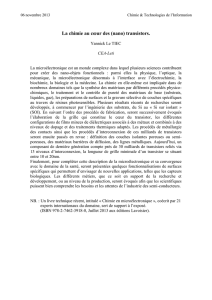

Par exemple, une présentation théorique du principe de

fonctionnement d'un modulateur Σ∆ du 2nd ordre tel que

celui représenté dans la figure 4 permet de faire apparaître

les sous-ensembles analogiques (les intégrateurs) et mixtes

(le comparateur et le Convertisseur Numérique/Analogique

(CNA)) de ce bloc.

∫ ∫

B

8 " 8"

C7

$

$

7

%7(

$)D

D

Fig. 4. Bloc diagramme du modulateur Σ∆ du 2nd ordre.

a.

!1

;E!,,,

;E!,,,,/

!,2**!,/

!1/

b.

!"

;E!,,,/

!,2 !%(

,.*F"2/

!,2 !%(

,.*F02/

/

!"/

c.

!""

;E!,,,/

,*F"2

!,**!/

,*F02

!,**!/

/

/

!"/

Fig. 5. Exemples simplifiés de descriptions comportementales des fonctions

(a) d'intégration, (b) de comparaison et (c) de CNA.

Des exemples de descriptions comportementales de ces

fonctions sont alors proposés (figure 5). Ces modèles sont

par la suite repris et affinés par les étudiants lors des séances

pratiques pour y intégrer la prise en compte des paramètres

divers tels que les gains, les dynamiques, les fréquences des

horloges primaires et secondaires etc.

Le découpage hiérarchique en sous-ensembles se prête

naturellement à la formation d'équipes, généralement des

binômes, qui se répartissent les tâches lors des séances

pratiques. Cette répartition tient compte de l'hétérogénéité

des sous-ensembles de manière à uniformiser le niveau de

difficulté sur l'ensemble de la promotion. L'une de ces

équipes est en outre désignée pour assurer la coordination

du projet. Cette désignation s'opère sur la base du

volontariat et concerne généralement l'équipe en charge de

l'assemblage du circuit au dernier niveau hiérarchique

MIGREST

P12

(assemblage final).

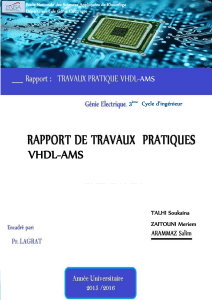

IV.RÉALISATION PRATIQUE DU PROJET

Les séances pratiques sont au nombre de six et se

déroulent au sein des locaux du pôle MIGREST, seul

organisme de la région Grand-Est disposant des outils de

CAO adéquats (Anacad®, suites d'outils Cadence® et

Altera®). Chacune représente un volume horaire de 4 heures

soit 24 heures au total. La mise en pratique des techniques

de conception d'un circuit intégré représente pour les

étudiants une double, voire triple, difficulté. Il s'agit d'une

part de mener un raisonnement de concepteur en

microélectronique, en l'occurrence les notions abordées

pendant les séances théoriques, d'autre part d'apprendre à

utiliser des outils propres au développement de circuits

intégrés, souvent lourds et complexes et enfin, pour certains,

de se familiariser avec l'environnement informatique

Unix/Linux.

La première séance est donc dédiée à la prise en main des

outils logiciels (Anacad®, outils Cadence®, environnement

Unix) et du langage VHDL-AMS par la description de

modèles simples. Les séances suivantes sont consacrées au

projet à savoir :

–Modélisation VHDL-AMS du modulateur Sigma-

Delta et simulation fonctionnelle.

–Modélisation hiérarchique et simulation des sous-

ensembles du bloc numérique.

–Implantation, prototypage sur FPGA (outils Quartus®

Altera®) et mise en place d’un banc de test des blocs

synthétisés avec des cartes NIOS® Cyclone® Altera®

et des modulateurs Sigma-Delta discrets.

Les étudiants travaillent en autonomie. Leurs activités

sont suivies par un encadrant maîtrisant le sujet du projet

dans sa totalité. Son rôle consiste à orienter la réflexion des

équipes sur les questions de conception et de modélisation

en VHDL-AMS et le cas échéant de leur apporter une

assistance technique sur l'utilisation des outils de CAO.

Chaque équipe (binôme) se consacre au développement

du sous-ensemble qu'il a choisi lors de la rédaction du

cahier des charges détaillé. Chaque étudiant dispose d'un

poste informatique équipé de tous les outils de CAO

microélectronique.

Le calendrier imposé aux étudiants est relativement

contraint puisque les travaux de modélisation et de

simulation des blocs individuels doivent impérativement

être menés à bien dans le temps imparti des séances 2, 3 et

éventuellement en début de séance 4. Celle-ci est

généralement consacrée à l'assemblage hiérarchique final et

aux simulations fonctionnelles mixtes et globales du circuit.

Les deux dernières séances sont quant à elles dédiées au

prototypage du système. Une maquette équipée d'un

modulateur Σ∆ discret 16 bits AD7720 ainsi que des cartes

de développement FPGA Cyclone et/ou Apex d'Altera® sont

mises à la disposition des étudiants. Les parties numériques

(FIR séquenceur, fonction « wattmètre », etc.) sont alors

implantées sur la cible FPGA à l'aide du logiciel Quartus.

La carte FPGA est interfacée avec le modulateur discret et

un afficheur LCD. L'ensemble est mis en œuvre et testé à

l'aide d'équipements de laboratoire standards (générateurs

basses fréquences, alimentations stabilisées, oscilloscopes,

etc.).

La figure 6 propose des exemples de réalisations

(organigramme fonctionnel, simulations analogiques et

numériques) effectuées par les étudiants.

a.

V

in

Intégrateur

Comparateur

Latch

CNA 1 bit

Horloge de

suréchantillonnage

CKS

Différence

D7

7

14%D7

(

14%7

(

G0

.0

"

0

"

0

D7

7

Signaux du modulateur Delta-Sigma

b.

Fig. 6. Exemples de réalisations, (a) organigramme et simulation analogique

du modulateur Σ∆, (b) simulation de la ROM du filtre.

V.CONCLUSION

Ce module de CAO microélectronique, proposé en

complément de leur spécialisation « Systèmes » permet aux

étudiants de l'INSA de découvrir un domaine, pourtant

voisin de l'électronique dite « conventionnelle » ou discrète,

qui leur est pour la plupart assez voire complètement

méconnu. Malgré un bagage initial en VHDL-AMS quasi

inexistant les 18 heures dévolues aux aspects théoriques

permettent d'explorer ce langage jusque dans ses subtilités.

Le projet de réalisation associé est particulièrement

motivant et les étudiants se prêtent volontiers à l'expérience

en formant spontanément des groupes de travail. Cette

configuration permet de les plonger dans une situation

proche de l'environnement professionnel auquel ils seront

confrontés. Selon le nombre d'étudiants, pouvant varier

quasiment du simple au double d'une année à l'autre (de 10 à

17 avec une moyenne de 12 étudiants par année), la

promotion peut être divisée en deux groupes de projets

amenés à développer en parallèle la conception de deux

circuits aux fonctionnalités identiques mais aux

architectures différentes, ce qui en soi représente une

expérience pédagogique supplémentaire.

RÉFÉRENCES

[1] Yannis Tsividis, Operation and Modeling of the MOS Transistor, 2nd

ed. , McGraw-Hill, Boston, 1999.

[2] Yannick Hervé, Vhdl-Ams - Applications Et Enjeux Industriels,

Cours Et Exercices Corrigés, Dunod, 2002.

MIGREST

P12

1

/

4

100%