TP&Cours encadrés par Mr. Lagrat Année universitaire 2016-2017

1

Rapport: Travaux pratiques sur VHDL-AMS ’ Génie Electrique

-AMS

3ème ’

VHDL-AMS

TALHI Soukaina

ZAITOUNI Meriem

Ecole Nationale des Sciences Appliquées de Khouribga

Département de Génie Electrique

TP&Cours encadrés par Mr. Lagrat Année universitaire 2016-2017

2

Rapport: Travaux pratiques sur VHDL-AMS ’ Génie Electrique

Remerciement

Nous avons ’

’ mes profondes gratitudes ainsi

que toutes mes reconnaissances à notre

professeur.

Nous remercions vivement Mr.

LAGRAT pour vos disponibilités, vos soutiens et

vos conseils, qui a créé une ambiance favorable qui

nous a per ’

nouveau parcours.

Enfin, que toute personne ayant contribuée

de près ou de loin à la préparation de ce travail,

’ nos profondes gratitudes.

TP&Cours encadrés par Mr. Lagrat Année universitaire 2016-2017

3

Rapport: Travaux pratiques sur VHDL-AMS ’ Génie Electrique

Table des matières

REMERCIEMENT …………………..…………………..…………………..………….…

Introduction générale …………………..…………………..…………………..

Partie 3: Boucle à verrouillage de phase (PLL)..………………..5

TP&Cours encadrés par Mr. Lagrat Année universitaire 2016-2017

4

Rapport: Travaux pratiques sur VHDL-AMS ’ Génie Electrique

Introduction générale

VHDL-AMS est un dérivé du langage de description matériel VHDL (norme IEEE 1076-

1993). Il comprend des extensions analogiques et des signaux mixtes (en anglais analog

and mixed-signal, AMS) afin de définir le comportement des systèmes à signaux

analogiques et mixtes (IEEE 1076.1-1999).

La norme VHDL-AMS a été instaurée dans l'intention de permettre aux concepteurs de

systèmes à signaux analogiques et mixtes et de circuits intégrés de pouvoir créer et

d'utiliser des modules qui encapsulent les descriptions de comportement de haut niveau,

aussi bien que des descriptions structurelles de systèmes et de composants1.

VHDL-AMS définit un langage de modélisation standardisé par l'industrie pour

les circuits à signaux mixtes. Il fournit à la fois le temps-continu et les sémantiques de

modélisation d'événements. Il est donc approprié pour les circuits analogiques,

numériques et mixtes. Il est particulièrement bien adapté pour la vérification de circuits

intégrés complexes qui allient des signaux analogiques, mixtes et des fréquences radios.

Il est important de noter que le VHDL-AMS ne constitue pas un langage de conception

ou synthèse. Il s'agit seulement d'un langage de description du matériel.

Ce TP a pour objectif de ’ ,

conception VHDL-AS, ’

TP&Cours encadrés par Mr. Lagrat Année universitaire 2016-2017

5

Rapport: Travaux pratiques sur VHDL-AMS ’ Génie Electrique

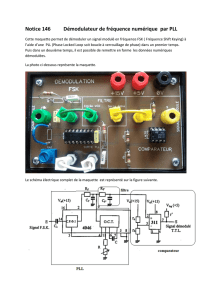

Partie 3 : Boucle à verrouillage de phase (PLL)

1. Introduction :

Les boucles à verrouillage de phase (Phase Locked Loop PLL) sont des circuits intégrés très utilisés en

. ’ ’ ’ asservissement de phase dont le rôle est

’ ’ à ’ . à

verrouillage de phase dans tous les équipements modernes.

2. Schéma de bloc :

-Les composants essentiels d’une PLL sont :

Un détecteur ou comparateur de phase - phase detector.

Un filtre de boucle passe-bas - low-pass filter.

Un oscillateur commandé en tension - voltage controlled oscillator (VCO).

un comparateur de phase (phase detector) est un circuit qui produit une tension de sortie

proportionelle à l'écart de phase entre le signal d'entrée et la sortie du VCO le comparateur de

phase décrit ci-dessous est construit à partir d'un circuit numérique composé de bascules D

(D flip-flops)

le fitre analogique est utilisé pour lisser le signal de sortie du comparateur afin d'obtenir sa

valeur moyenne le filtre passe-bas est un circuit RC de premier ordre

le circuit à boucle de phase quand on utilise la technologie CMOS, le VCO peut être

implémenté par un oscillateur booléen (ring oscillator) avec inverseurs différentiels dans notre

description le VCO est décrit au niveau comportemental

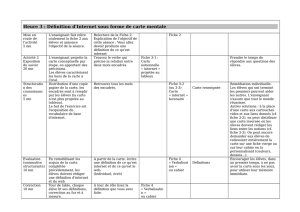

Détection d’évènements analogiques:

Pour décrire un comparateur ou un convertisseur A/D, il est nécessaire de détecter avec précision le

franchissement des seuils de quantification par le signal ’. F présente le

’ à hystérésis de seuils V1 et V2 et de niveaux hauts et bas : Vdd et

Vss.

6

6

7

7

8

8

9

9

10

10

1

/

10

100%