ppt

François ANCEAU

francois.anceau@polytechnique.fr

htt://lmi17.cnam.fr/~anceau/Doc.html

Une technique de réduction de la puissance

dissipée par l'horlogerie des circuits

complexes rapides

FTFC'2003

FTFC, © F. Anceau, 16 mai 2003 2 FTFC.ppt

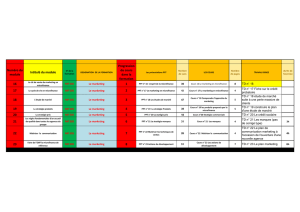

Evolution de la complexité

Nb Tr

I8008

MC6800

I4004

I8086

MC 68000

MC68020

Pentium-Pro

Pentium

I386

I286

PPC620

PPC601

MC68040 I486

Pentium II

Celeron

Pentium 4

1 000

10 000

100 000

1 000 000

10 000 000

100 000 000

1966 1971 1976 1981 1986 1991 1996 2001

INTEL

MOTO / IBM

FTFC, © F. Anceau, 16 mai 2003 3 FTFC.ppt

Evolution des performances

386/16

486/25486/50

PENTIUM-PRO/133

PENTIUM/133

PENTIUM/66

ALPHA/300

ALPHA/150

PPC 601/66

PPC 604/133

Millions d'instructions exécutées par seconde

(specint 92)

PENTIUM II/330

PPC 750/350

PENTIUM 4/1,5G

1

10

100

1000

10000

84 86 88 90 92 94 96 98 00 02

Intel

PPC

DEC

FTFC, © F. Anceau, 16 mai 2003 4 FTFC.ppt

Evolution technologique

0,01

0,1

1

10

100

1960 1970 1980 1990 2000 2010 2020

Taille des motifs minimaux (microns)

prédiction Intel 25nm

FTFC, © F. Anceau, 16 mai 2003 5 FTFC.ppt

Evolution de la fréquence d'horloge (X86)

(Ghz)

F horloge Micro Intel X86

50 Ghz

10 Ghz

prédiction Intel

24Ghz

Fréquence

externe

Fréquence

interne

Fréquence

bus

Utilisation de multiplieurs

de fréquence internes

1

10

100

1 000

10 000

100 000

75 80 85 90 95 00 05 10

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

1

/

22

100%