version PDF - Flash informatique

FI 7 – 25 septembre 2007 – page 1

Prochaines Parutions

no délai Parution

rédaction

8 04.10.07 23.10.07

9 01.11.07 20.11.07

10 29.11.07 18.12.07

sommaire

Fi 7/2007

1 La saga HP-35

François Roulet

2 DIT-info

3 Chiffres animés

Laurent Kling

7 Du bon usage du réseau

Jacques Virchaux

12 Memoria-Mea, ou comment

stocker, … ses informations

multimédias personnelles

Anne Le Calvé,

Elena Mugellini,

Hatem Ghorbel et

Philippe Richard

15 MailCleaner pour tous

Martin Ouwehand

16 vvpd – véritable vidéo à la

demande: patching

Andrés Revuelta

19 Prochain évènement CHOSUG

20 Programme des cours

24 Un nouveau certificat pour le

serveur RADIUS

Jacques Virchaux

suite en Page 8

La saga HP-35

Francois.Roulet@epfl.ch, Domaine IT

Préambule

Il y a 35 ans, apparaissait la pre-

mière calculatrice scientifique de po-

che, la HP-35, ainsi dénommée pour

son imposant nombre de touches.

Comme le déclarait la publicité, c’était

la première calculatrice de poche à

franchir le mur des 4 opérations, en

offrant les fonctions trigonométriques,

exponentielles et logarithmiques. Pour

cela, elle fût surnommée la tueuse de

règles à calcul.

Hewlett-Packard a célébré cet évé-

nement numérique, en annonçant en

juillet dernier le modèle commémoratif

HP-35s.

chronologie

1968 Premier calculateur scientifique

de table: HP-9100

1971 Premier microprocesseur: Intel

4004

1972 Première calculatrice scientifique

de poche: HP-35

1975 Premier micro-ordinateur helvé-

tique: Smaky

1977 Premier micro-ordinateur popu-

laire: Apple II.

Replaçons-nous brièvement dans le

contexte de cette époque.

Le premier calculateur scientifique

de table, le HP-9100, apparu en

1968, avait l’aspect d’une machine à

écrire électrique, hormis son clavier

qui n’était pas alphanumérique. Ce

qualificatif de Calculateur était stra-

tégiquement choisi par Bill Hewlett

afin de clairement se démarquer des

Ordinateurs du concurrent IBM.

Le HP-9100A marquait une étape

importante, en offrant le calcul en vir-

gule flottante et les fonctions transcen-

dantales, ainsi que la programmation,

tout en tenant aisément sur un bureau.

FI 7 – 25 septembre 2007 – page 8

Il était aussi caractérisé par l’absence de circuits intégrés, par

une mémoire vive ferrite, et une mémoire morte câblée et

gravée.

Suite à cette innovation, Bill Hewlett a chargé ses ingé-

nieurs d’en développer une version 10 fois plus petite (gabarit

d’un paquet de cigarettes taille royale), 10 fois plus légère

(255g au lieu de 18kg) et 10 fois moins chère ($395 au lieu

de $4900), et il ajouta encore qu’elle devait tenir dans la

poche d’une chemise. La HP-35 a relevé cet ambitieux défi,

tout en intégrant en première mondiale virgule flottante et

fonctions transcendantales (trigonométriques, logarithmi-

ques et exponentielles).

Pour parvenir à une telle prouesse, il fallait vraiment

faire preuve de génie, et c’est pourquoi nous souhaitons vous

présenter un certain nombre de solutions originales qui ont

présidé la genèse de cette formidable machine, précurseur

d’une légendaire lignée de calculatrices, assurant gloire, pres-

tige et fortune à la firme. Mais l’autre défi était de contrer les

Japonais sur le terrain des calculatrices à 4 opérations, qu’ils

monopolisaient mondialement.

Alors que l’ambitieux Bill Hewlett souhaitait vendre

10’000 exemplaires durant la première année, ses conseillers

commerciaux ont tenté de l’en dissuader, argumentant qu’un

instrument de calcul coûtant 20 fois le prix d’une règle à

calcul n’aurait aucune chance d’atteindre un tel objectif.

L’histoire a donné raison au premier, car 100’000 unités

ont été écoulées durant la première année, et au total 300’000

au cours des 3.5 ans de sa production.

Il faut se rappeler qu’à cette époque, une vulgaire cal-

culatrice 4 opérations était vendue en Suisse 444.- chez

InterDiscount !

La HP-35, initialement commercialisée à $395, avec un

taux de change de 3.9 CHF/$, était proposée en Suisse aux

alentours de 2000.- CHF.

La première caractéristique exclusive d’une calculatrice

HP était son mode d’introduction breveté des opérandes,

baptisé notation polonaise inverse, suite à l’invention en 1920

de la syntaxe postfixée par le Polonais Jan Lukasiewicz. Mais

en réalité, la description appliquée à l’informatique, qui est

due à l’Australien Charles Hamblin, a été publiée en 1957.

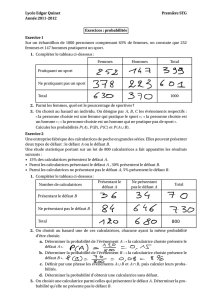

T

Z

Y

X

t

z

y

x

ENTER

y / x

T

Z

Y

X

t

z

y

x

y + x y - x

y . x

+ - x /

Les 2 principaux mouvements de la pile opérationnelle, à savoir

l'entrée d'un opérande, suivi d'une des 4 opérations

L’architecture interne de la gamme des calculatrices HP

n’a quasiment pas varié jusqu’à l’avènement de la HP-18C

en 1986, à tel point que la calculatrice financière HP-12C,

apparue en 1981 et actuellement toujours commercialisée (à

un tarif prohibitif), possède encore la même architecture que

la HP-35, à savoir une pile opérationnelle de 4 registres de

10 digits (56 bits chacun). Celle-ci détient le record histori-

que de longévité de produit et d’unités vendues par HP.

architecture

La HP-35 est fondamentalement caractérisée par une

représentation numérique BCD (Binaire Codé Décimal),

avec une mantisse de 10 chiffres significatifs et exposant

à 2 chiffres, et toutes les données sont mémorisées dans la

désormais célèbre pile opérationnelle, constituée de 4 re-

gistres à décalage, plus un registre mémoire indépendant

pour y déposer par exemple une constante. Deux registres

généraux, invisibles à l’utilisateur, sont affectés aux résultats

intermédiaires durant les opérations de calcul, et aux for-

matages et masquage des nombres durant l’affichage. Le jeu

d’instructions comporte 54 instructions distinctes codées sur

10 bits, les 8 premiers bits des instructions de branchement

étant réservés à l’adresse.

Le matériel est plus surprenant, car avec ce processeur

entièrement sériel, aussi bien l’adressage et l’accès aux ins-

tructions du microprogramme que les mouvements et les

calculs sur les registres s’effectuent toujours sur une seule

ligne. Les chemins de circulation des instructions et des

données étant totalement séparés, ce processeur respecte le

modèle de Harvard.

La sérialisation de tous les transferts d’informations

entraîne un temps de cycle très élevé de 280µs, alors qu’en

comparaison, le premier microprocesseur monolithique de

l’histoire, le Intel 4004, avait un temps de cycle de 10µs

seulement.

À y regarder de plus près, le processeur spécialisé d’HP

s’avère pourtant plus efficace, en évitant les lectures & écri-

tures en mémoire pour chaque chiffre à traiter, puisque les

registres sont exclusivement manipulés comme des registres

à décalage. Le temps de cycle est alors dicté par la circula-

tion complète du contenu d’un registre, soit l’équivalent

de 14 chiffres (10 pour la mantisse, 2 pour l’exposant et 2

pour les signes).

Avec une horloge à 200 kHz, en découlent un bit time de

5µs, un digit time de 20µs, et un word time de 280µs.

Afin d’optimiser la propagation de la retenue addition-

nelle, les registres sont naturellement exclusivement décalés

de gauche à droite, le chiffre le moins significatif défilant

en premier en direction de l’unité arithmétique et logique.

Inhérente à cette architecture sérielle, l’instruction lue et dé-

codée durant un cycle complet du processeur, ne sera traitée

que durant le cycle suivant. Toutefois, ce décalage temporel

n’affecte heureusement pas la rapidité de la machine.

suite de la Première Page

La saga HP-35

FI 7 – 25 septembre 2007 – page 9

Le mot mémoire, ou registre, comportant des champs

spécifiques (mantisse, exposant), il est impératif de pouvoir

les adresser individuellement, et cela s’effectue au moyen

du signal Word Select, qui sélectionnera temporellement la

portion du registre à décalage à traiter, et ce, aussi bien durant

un transfert, une copie ou une addition.

Cette approche entièrement sérielle minimise les in-

terconnexions, donc, les portes logiques requises pour la

réalisation du processeur.

réalisation matérielle

Le processeur de la HP-35 est principalement constitué

de 2 circuits intégrés, le circuit Control & Timing couplé

au circuit Arithmetic & Registers. Les trois autres circuits

intégrés sont les ROM renfermant le microcode de la calcu-

latrice. Chaque circuit comporte environ 6000 transistors,

tous les 5 totalisant le nombre impressionnant pour l’époque

de 30000 transistors. Leur fabrication fut confiée à 2 jeunes

fonderies de la Silicon Valley, AMI et Mostek.

La technologie LSI (Large Scale Integration) adoptée est

de type pMOS (Metal Oxide Semiconductor), nécessitant le

rafraîchissement permanent des données, obtenu par une

perpétuelle recirculation des registres à décalages, même

lorsqu’aucune opération ou mouvement n’est requis.

La technologie naissante CMOS exigeait trop de transis-

tors pour pouvoir être envisagée dans des circuits d’une telle

ampleur avec les processus de fabrication de l’époque. Un

des circuits est plus imposant, le Control & Timing avec ses

28 pattes requises notamment pour assurer le balayage du

clavier de 35 touches réparties en 5 colonnes de 8 rangées. Il

prend en charge toutes les instructions d’adressage, alors que

les instructions de données sont entièrement traitées par le

circuit Arithmetic & Registers. Ce second circuit constitue la

mémoire vive du calculateur, puisque la totalité des données

est mémorisée dans les 7 registres à décalage de 56 bits qu’il

renferme. Étant donné que toutes les interconnexions sont

sérielles, ce dernier ne comporte que 16 pattes.

Pour des raisons techniques, le reste de la circuiterie, à

savoir les pilotes des anodes et cathodes de l’affichage à diodes

électroluminescentes, est en technologie TTL.

Lors de l’avènement de cette architecture originale, le pre-

mier microprocesseur généraliste monolithique historique, le

Intel 4004, avait 6 mois d’existence, et l’on peut se poser la

question pourquoi ne pas avoir eu recours à ce matériel.

Ce processeur 4 bits pMOS d’architecture Harvard à

jeu de 46 instructions, mais à accès multiplexés sur 4 bits,

totalisait 2300 transistors. Avec son temps de cycle de 10µs,

il parait 28 fois plus rapide que celui de la HP-35 !

La réalité est bien différente, et l’on découvre tout le

bénéfice tiré de l’architecture originale et spécialisée choisie

par HP. Si le temps de cycle de la HP-35 est bel et bien de

280µs, il faut considérer qu’en ce laps de temps, un registre

est intégralement traité.

Typiquement, l’addition de 2 mantisses alignées de 10

chiffres sera entièrement accomplie durant ce word time !

Quant à lui, en un cycle, le 4004 ne pourra qu’addition-

ner 2 chiffres, l’un étant déjà préalablement chargé dans un

registre interne.

Pour replacer le résultat en mémoire centrale, il faudra

comptabiliser un cycle supplémentaire, et nous atteindrons

alors 20µs, soit exactement le digit time de la HP-35. Mais

le traitement du chiffre suivant exigera la lecture de l’ins-

truction, le chargement dans le registre 4 bits interne de la

donnée, puis l’addition proprement dite.

La saga HP-35

FI 7 – 25 septembre 2007 – page 10

De ce point de vue, il apparaît évident que l’architecture

de la HP-35 sera sensiblement plus efficace, donc perfor-

mante, que celle du 4004.

chronogramme

Dans le même domaine d’application, la plus célèbre

réalisation autour de l’Intel 4004 demeure la calculatrice de

table japonaise Busicom, dotée d’une imprimante intégrée,

mais strictement restreinte aux 4 opérations en virgule fixe,

et ressemblante aux caisses enregistreuses électroniques.

algorithmes

Alors que les 4 opérations s’effectuent de manière natu-

relle, il faut toutefois gérer la virgule flottante.

Pour l’addition et la soustraction, le temps moyen d’exé-

cution est de 60ms, cette durée découlant de l’alignement

des mantisses, mais aussi de la normalisation et du formatage

du résultat.

Pour la multiplication et la division, le temps moyen

d’exécution est de 100ms, cette durée découlant principale-

ment de la longueur de la mantisse, c’est-à-dire du nombre

de chiffres significatifs à traiter.

Mais le véritable tour de force réside dans le traitement

des fonctions logarithmiques en 200ms et trigonométriques

en 500ms seulement.

Pour les fonctions exponentielles et logarithmiques,

l’algorithme utilisé est celui des pseudodivision et pseudo-

multiplication décrit par J. E. Meggitt en 1962, découlant

de la méthode des différences publiée en 1624 par le mathé-

maticien anglais Henry Briggs.

Quant aux fonctions trigonométriques, elles sont effec-

tuées par des rotations CORDIC (COordinate Rotation

DIgital Computer), algorithme implémenté en 1960 par

Jack E. Volder dans le calculateur de navigation embarqué

du bombardier Convair B58 Hustler. Il s’agit d’approxima-

tions successives.

Le responsable de cette implémentation pour la HP-35,

David S. Cochran, fut surnommé le brasseur d’algorithmes.

les bogues

L’histoire de la HP-35 fut émaillée par le bogue émergeant

e^ln(2.02)=2 affectant les fonctions exponentielles. Il

n’est d’ailleurs pas sans nous rappeler le célèbre Pen-

tium Bug, qui a frappé les processeurs Intel en 1994,

quand bien même l’origine du second découlerait des

cœfficients erronés chargés dans la table de multipli-

cation, alors que le premier était dû à l’exécution de

l’algorithme, donc dépendant du microcode.

La correction de ce microcode fut un défi, car la

mémoire ROM de 768 mots était déjà entièrement

pleine.

Un autre bogue, affectant les fonctions trigonométri-

ques inverses, était moins perceptible, car l’erreur n’était

pas d’un pour cent, mais seulement d’un centième de

pour cent. Lorsque ces bogues furent signalés, et malgré

l’absence du vecteur de communication Internet, sur

ordre de Dave Packard, HP a réagi en proposant le re-

tour en usine pour échange gratuit des ROM des 25000

modèles défectueux déjà vendus. Malheureusement,

seul un quart des propriétaires se sont manifestés, ce

qui laisse encore bien quelques modèles défectueux en

circulation, aisément reconnaissables à leurs touches de

fonctions banalisées, leur fonction étant directement gravée

sur le boîtier.

aFFichage

Un soin tout particulier a été apporté à ce module, car

l’autonomie de cette calculatrice sur ses accumulateurs NiCd

devait lui permettre d’être utilisée hors raccordement au

chargeur secteur. Le nombre important de chiffres affichés

ayant une influence néfaste sur cette consommation, HP

a saisi l’occasion de mettre en application un brevet sur

les affichages à diodes électroluminescentes qu’ils avaient

précédemment déposé.

Pour la majorité des affichages de ce type, multiplexés

afin de minimiser le nombre de connexions, chaque diode est

alimentée au travers d’une indispensable résistance de charge,

qui dissipe de l’énergie durant l’illumination.

Le brevet d’HP consiste à contourner ce gaspillage, en

remplaçant le câblage conventionnel par l’établissement

préalable d’un courant dans une inductance, cette dernière

étant dans une seconde phase reliée en série avec la diode,

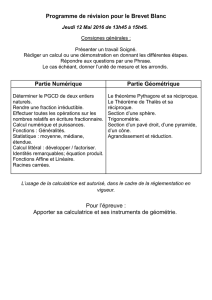

On distingue ligne après ligne, la synchronisation (SYNC) du cycle complet,

la lecture de l'instruction (Is), l'adressage de la mémoire morte (Ia), 3 des

8 variantes possibles de sélection de champ (WS), le contenu d'un registre

complet, soit 14 digits, 56 bits, le tout dans une fenêtre de temps de 280µs.

La saga HP-35

FI 7 – 25 septembre 2007 – page 11

induisant le courant nécessaire à l’illumination pulsée de la

diode. Dès lors, l’intensité lumineuse n’est plus déterminée

par la résistance de charge, mais par la durée d’établissement

du courant de charge dans l’inductance.

Grâce à cette astucieuse technique de pilotage, la consom-

mation de l’affichage demeure inférieure à 110mW avec tous

les segments allumés, la principale dissipation thermique

étant ainsi épargnée.

Pour garantir un chronogramme approprié, l’affichage est

le module qui requiert la cadence d’horloge la plus rapide de

toute la calculatrice, soit 800kHz, cela expliquant pourquoi

c’est précisément cet élément qui donne le pouls à tous les

autres circuits. En effet, le temps de charge de chacune des

7 inductances de segment n’est que de 2.5µs, (et la moitié

seulement pour celle du point décimal, sa surface lumineuse

étant nettement inférieure). Chacun des 7 segments d’un

chiffre est allumé séquentiellement à intervalle de 1.25µs,

afin de lisser la consommation de courant durant la phase

d’affichage de chaque chiffre. Le temps de décharge de chaque

inductance au travers de la diode luminescente est physique-

ment le double du temps de charge, soit 5µs.

Le séquencement de l’affichage se déroule en parfait

synchronisme avec la perpétuelle recirculation du registre

x; il est de fait entièrement rafraîchi en 280µs, en débutant

par le chiffre le plus à droite, l’exposant, pour terminer par

le signe de la mantisse à l’extrême gauche.

Un 15e symbole, le point décimal, est généré au vol par le

chronogramme de l’affichage, lui réservant un emplacement

complet sans pour autant prolonger le cycle d’une tranche de

temps. Cette particularité était aussi une exclusivité d’HP: le

point décimal occupant une position égale à celle d’un chiffre,

conférant ainsi une meilleure lisibilité des nombres.

clavier

Là aussi, les calculatrices HP se distinguent de leurs

concurrentes par leur clavier à touche basculante et rétroac-

tion tactile, fonctionnant selon le principe de la burette

d’huile, à savoir que l’élément de contact, assurant aussi la

fonction de ressort de rappel, constitué d’une cloque métal-

lique, cède soudainement au-delà d’une certaine pression

exercée sur la touche, retournant à l’utilisateur une sensation

tactile confirmant la prise en compte de l’ordre donné.

conclusion

Hewlett-Packard fut le grand innovateur parmi les

constructeurs de calculatrices électroniques. Le caractère

élitiste et la qualité permise par les prix pratiqués, a valu à HP

un cortège restreint, mais actif de fanatiques. Aujourd’hui, ces

calculatrices scientifiques semblent détrônées par l’omnipré-

sence des ordinateurs portables et des assistants personnels,

ces derniers supportant d’authentiques émulations des HP

récentes les plus diffusées.

Depuis, les utilisateurs d’antan se sont mués en col-

lectionneurs, et ces anciennes calculatrices atteignent des

prix astronomiques: la première version de la HP-35 avec

son point rouge caractéristique à côté de l’interrupteur se

négocie à $300.

Si nous devons référencer une exceptionnelle source

d’information consacrée à la HP-35, c’est sans aucun doute

le site Web de Jacques Laporte, une contribution historique

inestimable, recensant tous les aspects de la conception de

la HP-35, tant matériels que logiciels, avec un simulateur de

microcode en Java, qui offre la possibilité d’analyser jusque

dans les moindres détails le déroulement de l’exécution des

algorithmes, et de découvrir l’origine exacte des fameux bo-

gues. Saisissons ici l’occasion de remercier et féliciter Jacques

Laporte pour son aussi précieux que fastidieux travail de

bénédictin (http://www.jacques-laporte.org). n

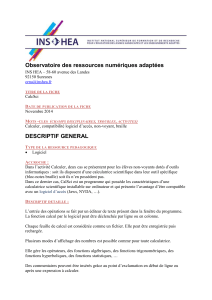

Classic Woodstock Topcat/Sting Cricket Spice Coconut Voyager

Scientific • HP-35

• HP-45

HP-46

• HP-55

HP-65

HP 9805

• HP-21

• HP-25

• HP-25C

HP-29C

HP-67

HP-91

HP-95C

HP-97

HP-97S

HP-19C

HP-31E

• HP-32E

HP-33E

• HP-33C

• HP-34C

• HP-41C

• HP-41CV

• HP-41CX

HP-10C

• HP-11C

• HP-15C

Financial HP-70

• HP-80

HP-81

HP-22 HP-92 • HP-37E

• HP-38E

• HP-38C

• HP-12C

Scientific/Financial HP-27

Other HP-10 HP-01

processor architecture Classic Woodstock Cricket Woodstock Nut

Tableau des modèles de la première génération, de 1972 à 1985, classés selon leur processeur interne (nonpareil.brouhaha.com)

La saga HP-35

1

/

5

100%