Micro électronique

MASTER PRO 2 EN TELECOMMUNICATIONS

MICRO ELECTRONIQUE

Séquence 1 : GENERALITES

Equipe des concepteurs :

- Jean KAMDEM

- Pierre TSAFACK

Le contenu est placé sous licence /creative commons/ de niveau 5 (Paternité, Pas d'utilisation

commerciale, Partage des conditions initiales à l'identique)..

REPUBLIQUE DU CAMEROUN

Paix - Travail – Patrie

---------------------

UNIVERSITE DE YAOUNDE I

----------------------

ECOLE NATIONALE SUPERIEURE

POLYTECHNIQUE

----------------------

REPUBLIC OF CAMEROUN

Peace - Work – Fatherland

--------------------

UNIVERSITY OF YAOUNDE I

--------------------

NATIONAL ADVANCED SCHOOL

OF ENGENEERING

--------------------

Getel / ENSP Master FOAD Télécommunications

Généralités

L’électronique moderne est une grande consommatrice de technologies

sophistiquées. Elle se subdivise en 2 parties essentielles :

- Le circuit imprimé (ou macroélectronique )

- La microélectronique

Le circuit imprimé est basé sur une technologie qui consiste à graver des

pistes conductrices sur un support isolant, puis à souder les différents

composants (passifs et actifs) sur les terminaisons de ces pistes, réalisant ainsi

les interconnections permettant de constituer un ensemble électronique

fonctionnel (monter une carte).

La micro-électronique s’occupe de la conception (CAO) et la fabrication de

circuits électroniques variés, sous un volume extrêmement réduit (plusieurs

centaines de composants par mm3 pour le circuit intégré).

La technologie micro-électronique est particulièrement développée. Elle

comprend les principales branches suivantes :

a. La technologie du composant discret qui consiste en la fabrication puis

la mise en boitier de transistors et diodes individuels.

b. La technologie du circuit hybride qui met en œuvre la gravure

directement sur un support isolant (généralement en Alumine), de

composants passifs (résistances, selfs, capacités) et des pistes

conductrices, puis effectue la soudure sur ce support de composants

actifs à l’état de chips (puces électroniques).

c. La technologie du circuit intégré (C.I) qui permet de réaliser à partir

d’un même substrat semi-conducteur (Si, CuAs, …) des fonctions

électroniques complètes incluant transistors, diodes, capacités, selfs,

résistances et interconnections métalliques, le tout sur une surfaces

allant de quelques mm² à quelques cm². On obtient alors un chip ou

une puce.

Le nombre de composants/chips peut varier de quelques milliers à plusieurs

centaines de milliers.

SSI (small scale integration) • 1000 par puce

Getel / ENSP Master FOAD Télécommunications

MSI (medium scale integration) 1000 à 10000

LSI (large scale integration) 10000 à n x 100000

VLSI (very large scale integration) 105 à plus de106.

La Silicon Valley aux USA est réputée pour son activité en circuits intégrés.

I. Les composants actifs dans les circuits intégrés

Les principaux composants actifs utilisés dans les circuits intégrés sont les

suivants :

- MOSFET

- FET

- Diodes (PN, Schottky, Photodiodes)

- Transistors bipolaires (PNP, NPN)

- Phototransistors

MICROELECTRONIQUE OPTOELECTRONIQUE

COMPOSANTS

DISCRETS

CIRCUITS INTEGRES

CIRCUITS HYBRIDES

BIPOLAIRES

(TRANSISTORS) MOSFET FET COUCHES

MINCES COUCHES

EPAISES

• MEMOIRES

• LOGIQUES

• ANALOGIQUE

• LINEAIRE OU NON

CCD

ET

BBD

MASTER PRO 2 EN TELECOMMUNICATIONS

MICRO ELECTRONIQUE

Séquence 2 : MODELISATIONDUMOSFET(METAL

OXYDESEMICONDUCTORFET),DELAJONCTIONP+N

ETDUTRANSISTORBIPOLAIRE.

Equipe des concepteurs :

- Jean KAMDEM

- Pierre TSAFACK

Le contenu est placé sous licence /creative commons/ de niveau 5 (Paternité, Pas d'utilisation

commerciale, Partage des conditions initiales à l'identique)..

REPUBLIQUE DU CAMEROUN

Paix - Travail – Patrie

---------------------

UNIVERSITE DE YAOUNDE I

----------------------

ECOLE NATIONALE SUPERIEURE

POLYTECHNIQUE

----------------------

REPUBLIC OF CAMEROUN

Peace - Work – Fatherland

--------------------

UNIVERSITY OF YAOUNDE I

--------------------

NATIONAL ADVANCED SCHOOL

OF ENGENEERING

--------------------

Getel / ENSP Master FOAD Télécommunications

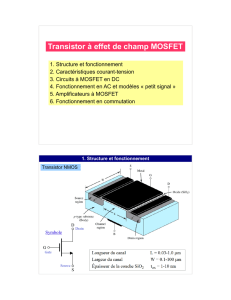

2- Modélisation du MOSFET (Metal Oxyde Semiconductor FET), de la

jonction P+N et du transistor bipolaire.

Le MOSFET est le composant le plus utilisé dans la réalisation des circuits VLSI

(processeurs – mémoires). Sur le plan discret, le MOSFET est aussi un

composant de puissance.

Structure de base

Substrat type P pour MOSFET canal N

Substrat type N pour MOSFET canal P

Analyse qualitative

Configuration du canal et de la charge d’espace pour de faibles valeurs de

VDS.

• Le métal de grille et le substrat P forment avec l’isolant de très faible

épaisseur d, un condensateur plan de valeur

• La d.d.p VGS > 0 entre la grille et le substrat provoque une migration des

électrons vers la surface du substrat sous la grille.

• Pour VGS = VT > 0, il se produit une inversion de population dans une

mince couche entre les 2 zones N+ (canal), le matériel qui était P

devient N dans le canal

• La d.d.p VDS provoque le passage d’un courant ID entre drain et source.

Vgs < VT ⇒ MOSFET bloqué ID = 0

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

1

/

63

100%