LES COMPOSANTS OPTOÉLECTRONIQUES J Microphotonique

LES COMPOSANTS OPTOÉLECTRONIQUES

J

Microphotonique silicium

pour connexions rapides

sur circuit intégré

Mots clés

Optique guidée,

Interconnexion,

Distribution

d'horloge.

Par J.-M. Fedeli', S. Laval**

. Chef de projet au CEA-LETI

** Directeur de Recherches CNRS à l'institut d'Électronique Fondamentale

Dans un futur proche, les circuits intégrés vont être limités dans leur

capacité à distribuer à grande vitesse les informations entre blocs qui

les composent. L'introduction de la distribution photonique de

l'information sur ces liens globaux est susceptible d'améliorer

le synchronisme dans la distribution d'un signal d'horloge,

tout en réduisant la puissance consommée, et de permettre

l'augmentation des débits.

1. Introduction

Le déploiement mondial des télécommunications

optiques à longues distances et à hauts débits a été un des

faits majeurs des deux dernières décennies. Histori-

quement, les solutions optiques se sont imposées par

rapport aux solutions électriques lorsque les pertes essen-

tiellement liées à la résistivité du cuivre et à l'augmentation

des débits de transmission sont devenues trop élevées.

Actuellement, les communications optiques résolvent la

. En microélectronique, les interconnexions électriques à

l'intérieur du circuit intégré constitueront un des goulots

d'étranglement dans l'augmentation des performances des

circuits intégrés du fait de la diminution des dimensions

transversales des liens électriques et de l'augmentation des

fréquences de fonctionnement.

. L'introduction de la distribution photonique de l'information

sur les liens globaux est susceptible d'améliorer le

synchronisme de la distribution d'information tout en

réduisant la puissance consommée, et aussi de relâcher les

contraintes de conception sur les niveaux les plus élevés de

métallisation (distribution d'horloge par exemple)

. L'architecture du système de connexion optique se compose

d'un ou de plusieurs émetteurs intégrés de lumière dans le

proche infrarouge couplés à un ensemble de guides optiques

intégrés qui réalisent une distribution optique. À l'extrémité de

ces guides, un ensemble de photodétecteurs intégrés sur

substrat silicium délivre électriquement le résultat de la

fonction optique.

plupart des problèmes liés aux goulots d'étranglement des

interconnexions et des limitations en vitesse de l'électro-

nique, en offrant une très grande bande passante, une

grande immunité au bruit, une réduction de la puissance

dissipée et de la diaphonie.

En parallèle, la technologie de la microélectronique

s'est développée à un rythme exponentiel au cours de ces

quarante dernières années. Cela s'est traduit par une minia-

turisation du transistor élémentaire et par une intégration

de plus en plus poussée de systèmes électroniques

SYNOPSIS

. Electrical connections inside VLSI chip will become one of

the bottlenecks for the increase in performances. This is due

to the shrinking of lateral dimensions of electrical links

concomitantto operation frequency rise.

. Optical distribution of data on global links may improve the

synchronism of the delivery while reducing the required

power, as well as freeing the routings on the higher metallic

layers (data clock delivery for instance)

. An optical connecting system is architectured using basic

blocks operating in the near infrared. Integrated light emitters

are coupled to silicon optical wave guides which constitutes

an optical distribution. At the end of these waveguides,

photodetectors transform the optical function results in

electrical signals which are processed by the underlying

integrated circuit.

1

REE

N° 9

OCIIIIIE 2u () 2

complexes. Les circuits ont alors augmenté de taille et la

complexité de transmission des données s'est traduite par

l'introduction de connexions multi-niveaux au sein des

circuits. Le problème de pertes dues aux connexions a

longtemps été négligeable, mais il commence à devenir

crucial au fur et à mesure de la diminution des dimensions

transversales des liens électriques et de l'augmentation des

fréquences de fonctionnement. Une des alternatives aux

liaisons électriques dites globales au sein des puces

silicium est de recourir à l'optoélectronique sur silicium

afin de diminuer la latence et la puissance consommée lors

de la transmission de données. Dans une vision plus

futuriste, l'application des techniques de routage multi-

fréquentiel utilisées dans les télécommunications optiques

pourrait augmenter les débits internes à l'intérieur des

puces.

2. Les limitations de vitesse

des circuits intégrés

Selon les prévisions de l'ITRS (International

Technology Roadmap for Semiconductors), à l'horizon

2005, les circuits intégrés (CI) de dimensions sub-O,l pm

devraient comprendre des centaines de millions de

transistors et travailler à des fréquences d'horloge de

plusieurs GHz. Les interconnexions électriques intra-chip

ou inter-chip (pour les « multi-chip modules » ou MCM)

constitueront l'un des goulots d'étranglement dans la

poursuite du progrès des performances des CI. Les limita-

tions apportées par les interconnexions métalliques sur

puce ont pour origine d'une part la diminution des dimen-

sions transversales des interconnexions métalliques, corré-

lative à l'augmentation de la fréquence de fonctionnement

des circuits, et d'autre part l'augmentation de leur densité.

Les liens concernés par ces limitations sont, certes, peu

nombreux (quelques centaines) et spécifiques (il s'agit des

liens dont la longueur est voisine de la dimension du

circuit : horloge, signaux de contrôle, certains bus) ; mais

les solutions mises en oeuvre pour pallier ces limitations

sont onéreuses et concernent à la fois la technologie et les

stratégies de routage des interconnexions ainsi que les

architectures de système. En effet selon le type de circuit

considéré (processeurs « standard » ou les systèmes sur

puces (SoC)), la gestion des flux de données diffère. Par

exemple, les circuits SoC contiennent quelques dizaines de

blocs spécialisés (unités de calcul, mémoires, DSP, inter-

faces vidéo...) dont les échanges sont organisés par l'inter-

médiaire de un ou plusieurs bus dont le routage est figé.

L'accroissement prévisible du nombre de ces blocs

imposera un nouveau procédé de communication reconfi-

gurable.

La diminution des dimensions des liens conduit à une

augmentation de la résistance linéique des pistes métal-

liques plus rapide que la réduction de leur capacité

linéique, et donc, à l'augmentation de la constante de temps

associée au transport du signal. L'augmentation des

fréquences de fonctionnement induit des contraintes

temporelles de transmission qui nécessitent d'équiper les

liens les plus longs de buffers et donc d'augmenter la

puissance dissipée par le circuit. Ainsi, par exemple, la

distribution de l'horloge peut absorber jusqu'à deux tiers

de la puissance consommée par un microprocesseur. Par

ailleurs, l'augmentation relative du temps de retard de la

transmission vis-à-vis de la période de l'horloge conduit au

phénomène de latence, et à celui, sans doute encore plus

pénalisant, de « skew » (c'est-à-dire de la variation du

retard de l'arrivée des signaux sur l'entrée d'une bascule,

en fonction de la position géographique de celle-ci sur le

circuit). Enfin, l'augmentation de la densité des intercon-

nexions métalliques conduit à des phénomènes de

diaphonie.

Les solutions à l'oeuvre pour repousser ces limites dans

les technologies actuelles concernent :

. la technologie de réalisation des intercollnexions : la

diminution de la constante de temps s'est traduite par la

mise en oeuvre des technologies cuivre et de matériaux

à faible constante diélectrique. L'augmentation des

dimensions des couches métalliques superficielles

diminue la résistance des pistes réservées au routage des

liens longs, d'où la solution d'augmenter le nombre de

couches de métallisation (7 à 8 niveaux d'intercon-

nexions métalliques pour les technologies 0, 1 p m). Les

techniques de refroidissement des circuits utilisées

actuellement pour les supercalculateurs, ou l'utilisation

de supraconducteurs, sont difficiles à mettre en oeuvre

dans un cadre non spécifique ;

. la stratégie de conception : les liens longs sont équipés

de répéteurs aux dépens de la consommation et les outils

de conception permettent de déterminer, très tôt dans le

cycle de conception, le temps de retard dû aux inter-

connexions et la diaphonie, de façon à adapter l'archi-

tecture du système.

3. Pourquoi des liens optiques

sur un circuit intégré ?

L'ITRS met en évidence que les solutions technolo-

giques concernant les interconnexions sont actuellement

inconnues pour les technologies sub-65 nm. En parallèle

avec les travaux permettant de repousser les limites prévi-

sibles (utilisation du cuivre et de matériaux à faible

constante diélectrique, nouvelles architectures et nouveaux

designs), des voies technologiques alternatives aux inter-

connexions métalliques classiques sont donc proposées

comme l'intégration 3D, les solutions RF ou les intercon-

nexions optiques.

L'introduction de liaisons optiques sur puce est

envisagée tout d'abord pour des liaisons point à points

(distribution d'horloge et de données bus). Ces liaisons

optiques ne se justifient que pour des liens longs dits

globaux au niveau de la puce (quelques centimètres sur une

puce) pour limiter les conversions électrique-optique-

électrique. L'avantage est de diminuer le « skew » et la

puissance consommée.

Dans un second temps et à l'instar des réseaux de

télécommunications actuels, l'exploitation du multiplexage

REF

N.')

0, 2 (02 1

Do,-,sOË LES COMPOSANTS OPTOÉLECTRONIQUES

en longueur d'onde devrait répondre sur les circuits

intégrés à la tendance permanente à l'augmentation du

débit dans les bus ainsi qu'au besoin pressenti pour un

réseau de communication standardisé entre blocs IP. Cette

approche se conçoit comme un objectif à long terme, ne

serait-ce que par les nouvelles architectures potentielles

dont l'étude reste à faire.

La distribution d'horloge est la première démonstration

à réaliser afin de valider l'apport des interconnexions

optiques sur puce pour les liens globaux. Actuellement ils

sont en général routés sur les niveaux supérieurs de métal-

lisation où il est possible d'atteindre des résistances

linéiques plus faibles. Le remplacement de l'arbre de distri-

bution métallique par un réseau optique permettra de

libérer les couches de métallisation supérieures et

d'améliorer ainsi la connectabilité du circuit, de contrôler

parfaitement le synchronisme de l'horloge et d'atténuer la

pollution électromagnétique des noeuds sensibles par

l'horloge : des étapes de conception onéreuses seront ainsi

allégées.

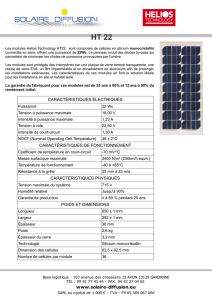

La distribution optique de l'horloge peut se faire sous

la forme d'un arbre en H (voir Fig. 1) constitué d'une

source de lumière délivrant l'horloge aux différents photo-

détecteurs des blocs via des guides optiques composés de

lignes, de courbes, de diviseurs.

oa Da

mmil.1mi Ili il 1 Ille

Dy D%..fl

1 eh - j-

Photodétecteur

de- Source lumineuse

Diviseur

Figure 1. Distribution optique d'horloge.

Quels sont les points caractéristiques de cette approche

technologique dont les composants de base en sont encore

au stade de la recherche ? Elles peuvent se résumer sous

un ensemble d'attraits potentiels, de difficultés et de

contraintes.

. Les contraintes :

- la compatibilité avec les futures technologies CMOS ;

- un surcoût de fabrication acceptable.

. Les attraits potentiels :

- le maintien du synchronisme par la réduction de la

gigue et du « skew » d'où la suppression des circuits

de synchronisation ;

- l'augmentation de la bande passante ;

- l'isolation électrique ;

- la réduction de la puissance consommée ;

- une moindre sensibilité à la température ;

- l'immunité aux bruits électromagnétiques ;

1

- la sortie optique de l'horloge vers d'autres circuits

fonctionnant en synchronisme.

Les difficultés :

- ta réduction des pertes sur les composants optiques

afin de permettre la distribution sur un grand nombre

de photodétecteurs ;

- ta densité des guides optiques sur la puce ;

- l'efficacité de la conversion électro-optique à la fois

sur la source et les photodétecteurs ;

- te fonctionnement des composants actifs dans la

gamme des dizaines de GHz ;

- ta minimisation de la latence sur les drivers et les

récepteurs.

En généralisant l'approche de la distribution d'horloge,

l'architecture du système de connexion optique se compose

d'un ou de plusieurs émetteurs couplés à un ensemble de

guides qui réalisent une fonction optique passive (ou, à

terme, dépendante d'une commande électrique). Ces

guides aboutissent sur un ensemble de photodétecteurs qui

délivrent électriquement le résultat de la fonction optique.

En France cette étude est soutenue par le ministère de

la recherche et les collectivités territoriales dans le cadre

de projets regroupant un consortium de laboratoires :

IEF/CNRS/UPS, LEOM/CNRS/ECL, LPM/CNRS/INSA,

IMEP/CNRS/INPG, CEA-DRFMC, CEA-LETI pour ne

citer que les acteurs principaux. Chaque laboratoire apporte

ses compétences spécifiques afin de développer plusieurs

voies de recherches pour les composants élémentaires.

4. Sources de lumière et modulation

Les types d'émetteurs envisagés sont soit de la famille

111-V reportés par hybridation sur silicium, soit directement

de type silicium.

Le principe utilisé avec les matériaux III-V est basé sur

l'utilisation de micro-dispositifs passifs en optique guidée

sur silicium sur isolant (SOI) et leur couplage vertical avec

des composants optoélectroniques actifs III-V (microlasers

et photodétecteurs résonants) reportés par collage molécu-

laire sur la plaque SOI. On reporte une couche composée

d'une hétérostructure InGaAs/InP qu'il convient de graver

afin de réaliser un confinement. Ce confinement peut se

faire sous forme de microdisques de quelques microns de

diamètre ou par gravure de trous formant ainsi une cavité

à cristaux photoniques. Ce confinement diminue le seuil

des microlasers par augmentation du confinement des

excitons dans la source. En fait, l'émission stimulée est

d'autant plus favorisée que la densité d'états convoluée

exciton-photon est importante dans le mode laser désiré.

Deux types de couches actives émettrices sont à l'étude :

les puits quantiques présentent l'avantage d'une techno-

logie mature tandis que les boîtes quantiques encore au

stade de la recherche, permettront le confinement optimum

des excitons et d'atteindre les seuils les plus bas.

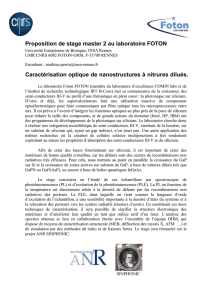

Il faut ensuite coupler cette microcavité laser aux guides

optiques sur SOI (Fig. 2). La source étant positionnée au-

dessus du circuit passif, le transfert de l'onde entre la

source et le circuit aval s'effectue vers un collecteur de

REE

NI 9

Octobre 2002

photons par couplage évanescent (flèche verticale) à

travers une couche de silice. Le signal optique est ensuite

couplé vers des guides d'onde (flèche horizontale sur la

Fig. 2) et est distribué sur la puce par le réseau de guides

optiques.

Une voie plus exploratoire est d'utiliser un émetteur en

silicium dopé (Er, Er-O, P...) confiné par cristaux photo-

niques. L'émission de lumière par un film de silicium est

a priori difficile. Le gap indirect du silicium (ou des

alliages Si,Gel-,) implique la participation de trois parti-

cules : électron, trou et phonon pour l'émission d'un

photon. Ce phénomène est peu probable et les durées de vie

des porteurs sont élevées (de 10-4 à 10-3 secondes). Les

énergies de liaisons des excitons sont faibles et leur disso-

ciation à température ambiante limite l'efficacité des

processus radiatifs. Les meilleurs rendements de lumines-

cence démontrés à ce jour sont de l'ordre du pour cent mais

concernent du Si poreux. Dans le cas du silicium mono-

cristallin, qui est le mieux adapté en terme d'applications

potentielles, il a très récemment été démontré qu'en

confinant des films minces de silicium (ou des alliages

SixGel-x) dans des barrières de matériau à grand gap,

comme la silice, on observait un net renforcement de la

quantité de lumière émise. Ces microstructures peuvent

être envisagées aujourd'hui grâce aux avancées du collage

moléculaire de films minces.

Les débits requis supérieurs à la dizaine de Gbit/s

peuvent rendre impossible la modulation directe au niveau

de l'émetteur. On peut alors envisager l'émission en

continu suivi d'un modulateur rapide commandé par effet

électro-optique. Les effets électro-optiques résultent du

changement des caractéristiques de réfraction d'un

matériau sous l'action d'une tension électrique appliquée.

En raison de la symétrie du réseau cristallin du silicium, la

modification du nombre de porteurs libres est le seul

mécanisme pouvant conduire à un effet électro-optique

dans ce matériau. Des électrons (ou des trous) peuvent être

injectés dans une région non dopée à l'aide d'une jonction

pn polarisée en direct, ou bien ils peuvent déserter une

région dans laquelle ils sont initialement présents. Les

temps de réponse pour l'injection électrique de porteurs

sont dans la gamme des u.s. Les dispositifs à désertion sont

beaucoup plus rapides. Le principe est alors de moduler

l'indice optique des matériaux par une variation de la

Source microphotonique

en microcavité \

Collecteur de photons

en silicium

distribution des trous en concentrant ces derniers dans des

puits dans la bande de valence d'hétérostructures

Si/SiGe/Si et en plaçant cette structure à l'intérieur d'une

jonction pn pour pouvoir dépléter les puits par application

d'une tension inverse. Cela conduit à deux états corres-

pondant à des indices optiques différents des couches SiGe,

donc à une modulation de phase qui est transformée en

modulation d'intensité en plaçant les couches actives dans

une cavité résonante, de type Fabry-Perot par exemple.

5. Guidage et fonctions optiques

La surface réduite des circuits intégrés ne permet pas

d'utiliser des guides optiques à faible contraste d'indice qui

nécessitent des rayons de courbure trop grands pour les

changements de direction. Il faut donc se focaliser sur les

dispositifs à fort contraste d'indice comme le silicium

associé à l'air ou à la silice. Cela se traduit soit par des

guides utilisant le film de silicium monocristallin des

substrats SOI, soit par des guides en silicium polycristallin

déposés en surface du circuit intégré terminé. La forte

différence d'indice de réfraction entre le silicium et la

silice conduit à un fort confinement du champ électroma-

gnétique dans le film de silicium du SOI servant de guide

d'onde (Fig. 3). Le confinement latéral est obtenu soit par

gravure totale du film de silicium, conduisant à des micro-

guides rubans de section inférieure à 0,4 ! lm x 0,4 ! lm

pour être monomodes, soit par gravure partielle du silicium

pour former des guides en arête, dont la largeur peut être

plus grande ( 1 p,m). Les performances actuelles sont de

0,3 dB/cm de pertes de propagation pour un guide en arête

de 380 nm d'épaisseur et de 1 lm de large et de 8 dB/cm

pour un guide ruban de 200 x 500 nm dans le cas du

silicium monocristallin. Les pertes de propagation

dépendent essentiellement de la rugosité de flancs des

guides. Les films de silicium polycristallin sont préparés

par LPCVD ou PECVD à partir de silane ou de disilane.

La difficulté est de pouvoir recuire le dépôt sans dégrader

les circuits afin d'en améliorer la qualité optique. Les

guides de 0,5 ! lm de largeur et de 0,2 ! lm d'épaisseur

fabriqués au MIT par LPCVD à 560'C avec un recuit de

cristallisation de 600 °C de 16 h suivi d'un recuit à 1100'C

de l6 h présentent une perte de 20 dB/cm.

Silice

7-- *--7

photons ---- ! WI/

r-- 1 11, 1-

- L- , 11

Guide d'onde

l'en silicium Silice

Sbàr4,t sih *

C-iIM, Figure 2. Couplage de la microcavité

laser aux guides optiques sur silicium sur

isolant.

REE

N'9

Octobre 2002

1

Ü

1

- --,'1 11- -. LES COMPOSANTS OPTOÉLECTRONIQUES

i

; ·_..

=.x ; l

âPT ` -`s

u^`

i

;

I, "' " ' " v r , :

''rt " ',,' ts`, " r'i l

_ vs'. c ' ; G W tr. n r. ; Y " "'1

, x.. P H, z.,. : °.. _, r=. '.' c

Figure 3. Mict-ocavité insei-i-ée dans tin gitide

(INSAILPM-LETI).

f

l

I

I

I

Les

f : J j

rcP'

I

i h

E m :

I

i

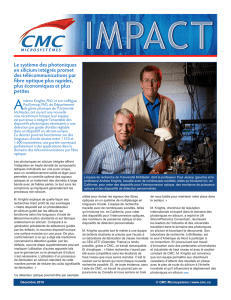

Figure 4. Diviselir 1 vers 4 (lEF - INSAILPM-LETI).

Le très fort contraste d'indice permet également de

réaliser des virages avec des rayons de courbure de l'ordre

du um (Fig. 4). Les miroirs obtenus par gravure totale du

film de silicium du SOI présentent de très faibles pertes, en

particulier pour les guides en arête. De plus, des diviseurs

de type MMI (MultiMode Interferometer) de 1 vers 4

montrent des sorties équilibrées pour un encombrement

réduit. La technologie des guides en arête sur SOI permet,

du fait des faibles pertes mesurées pour les différents

éléments passifs (guides, miroirs, diviseurs de faisceaux)

d'envisager de façon réaliste la distribution d'un signal

c

d'entrée vers 16 blocs dans un schéma de distribution

d'horloge tel que celui décrit sur la figure 1.

6. Photodétection

Comme pour les sources, deux alternatives se

présentent, avec soit l'utilisation de détecteur IV-IV

absorbant dans la gamme 1,2 - 1,5 u.m, soit le report de

matériau 111-V sur le circuit silicium.

La première est basée sur l'utilisation de couches à base

d'alliages IV-IV (SiGeC, multi-puits quantiques SiGe/Si,

Ge pur...). L'absorption dans la gamme 1,3-1,5 pm

nécessite une incorporation de Ge à un taux élevé dans les

couches. Pour des longueurs d'onde autour de 1,3 D.m, la

réalisation de multicouches SiGe est envisageable à

condition d'incorporer 40 % de Ge pour obtenir une

absorption suffisante. Le Ge pur présente une absorption

supérieure. Pour les applications à 1,5 D.m. des boites

quantiques en Ge dans des couches de Si est une voie

prometteuse. Par ailleurs, les options possibles portent sur

la nature des contacts (diode PIN ou MSM), leur géométrie

(contacts latéraux ou verticaux, interdigités ou non), le

type de couplage avec la lumière guidée (en bout ou

évanescent). Les performances de rapidité requises impli-

quent une photodiode de taille réduite pour diminuer le

temps de transit des porteurs photogénérés et la capacité de

la jonction. La longueur de matériau absorbant étant

réduite, la sensibilité de détection sera accrue en plaçant la

zone active en surface ou dans une microcavité optique de

type Fabry-Pérot à miroirs de Bragg, compatible avec le

guide SOI et accordée à la longueur d'onde de la diode

laser. Les miroirs de Bragg sont constitués de fines fentes

gravées dans le guide SOI. Le fort contraste d'indice fait

qu'il suffit d'un petit nombre d'alternances pour obtenir

une réflectivité importante et permettre ainsi la réalisation

de microcavités de dimensions microniques avec une

finesse élevée. Les couches détectrices sont placées en

surface de cette microcavité dans le cas d'un couplage

évanescent.

La deuxième voie est constituée par des photodiodes

PIN de type large bande à base d'hétérostructures III-V

InP/GaInAsP. Elles sont rapportées par collage molécu-

laire au-dessus d'un réseau de découplage placé à

l'extrémité du guide Si. Ce réseau permet d'extraire la

lumière en la diffractant verticalement vers la photodiode.

Le report par adhésion moléculaire étant une technique

bien maîtrisée au LETI, la difficulté vient de la fabrication

des contacts supérieurs et inférieurs dans une telle structure

à dimensions latérales faibles (de l'ordre de 5 n,m).

7. Conclusion

Si les attraits potentiels des interconnexions optiques

sont bien réels pour résoudre le goulot d'étranglement en

vitesse des liens globaux sur les circuits intégrés, de

nombreuses démonstrations de la fonctionnalité des

1

6

6

1

/

6

100%