Interconnexions optiques pour les systèmes sur puce (SoC)

DISPOSITIFS DE L’ELECTRONIQUE INTEGREE

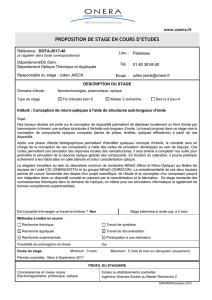

STAGE DE RECHERCHE

Nom et Adresse du Laboratoire d’Accueil :

Laboratoire d’Electronique Optoélectronique et Microsystèmes, LEOM -Ecole Centrale de

Lyon

Nom du Directeur du Laboratoire :

G. Hollinger

Nom du Responsable Scientifique du Stage :

I. O'Connor

N° de Téléphone : 04 72 18 60 54 N° de Fax : 04 78 43 35 93

e-mail : ian.oconnor@ec-lyon.fr

Titre du Stage Proposé : Interconnexions optiques pour les systèmes sur puce (SoC) :

modélisation de réseaux de routage en longueur d’onde

Option(s) du DEA concernée(s) : 1 (composants), 2 (circuits)

Programme résumé des Recherches :

L’ITRS (International Technology Roadmap for Semiconductors), montre que dans une dizaine

d’années, des systèmes intégrés seront conçus qui intégreront plusieurs dizaines de millions de

transistors. La complexité de tels systèmes remet fondamentalement en cause les méthodes actuelles

de conception. Cela nécessitera notamment le développement de nouvelles technologies pour les

communications on-chip. Les interconnexions optiques sont aujourd’hui la voie la plus prometteuse

pour répondre aux besoins en terme de bande passante, de consommation et de densité d’intégration.

Cela passera par le développement de circuits intégrés photoniques dotés de sources lumineuses, de

guides de lumières, de composants de routage et de photodétecteurs de dimensions microniques

(Microphotonique). Un des intérêts fondamentaux de l’optique réside dans la possibilité de coder

l’information en longueur d’onde (WDM), ce qui ouvre la voie à la réalisation de réseaux optiques

reconfigurables. Le composant clef de ces systèmes est le filtre directif et sélectif (Add-Drop), qui

permet le multiplexage/démultiplexage en longueur d’onde.

Ce projet poursuit un double objectif :

- développer des modèles comportementaux de haut niveau permettant la simulation rapide

de structures de réseaux de routage. Il s'agit de modéliser de manière fonctionnelle les

diverses topologies de réseau existants, et ensuite de valider ces modèles par comparaison

avec la théorie et simulation par différences finies. Ce travail facilitera l'exploration des

architectures susceptibles de réaliser la fonction du réseau.

- explorer des méthodes de simplification des modèles pour simulation compatible avec un

système complet, ainsi que des méthodes de spécification des blocs pour conception à un

niveau plus détaillé.

Ce travail sera réalisé dans le cadre d’un programme de recherche auquel sont notamment associés

ST-Microelectronics et le LETI-CEA.

Poursuite en thèse : o OUI o NON

1

/

1

100%