PCI Express

46 MESURES 769 - NOVEMBRE 2004

S

olutions

L’

interface d’entrées/sorties PCI

(Peripheral Component Interconnect) a

déjà plus de 10 ans.Introduit au

début des années 1990, le bus

PCI a eu comme premier effet d’unifier l’ar-

chitecture d’interconnexion des périphé-

riques du PC, sur un marché qui comptait

alors une multitude de bus différents :VESA,

EISA,ISA,Micro Channel,NuBus,Sbus,etc.

Il fut d’abord mis en œuvre en tant que sys-

tème d’interconnexion

de circuit à circuit et

remplaça très rapide-

ment le bus ISA

(Industry Standard

Architecture) et ses

dérivés.Durant les pre-

mières années,dans sa

version initiale

(32 bits/33 MHz), ce

bus répondait parfaite-

ment aux exigences

des périphériques

d’entrées/sorties de

l’époque en terme de

bande passante. Il

apportait également un

grand nombre de

nouveautés par rapport

aux précédentes inter-

faces comme l’indépendance vis-à-vis du

processeur, l’isolation bufférisée, le fonction-

nement en mode maître d’un périphérique

et la reconnaissance plug and play des nouvelles

cartes.En particulier,l’isolation buffériséea per-

mis d’isoler le bus PCI du bus local du pro-

cesseur,électriquement mais aussi en terme

d’horloges.Cela s’est traduit par deux consé-

quences fondamentales pour l’amélioration

des systèmes : la possibilité d’effectuer des

cycles simultanés sur les deux bus et celle

d’augmenter la fréquence du bus processeur

sans avoir à modifier la vitesse et la charge du

bus PCI.

Des évolutions qui ont

aussi des limites

Toutefois, aujourd’hui, la situation a beau-

coup évolué.Les fréquences de fonctionne-

ment des processeurs et des mémoires ont

considérablement augmenté. Certes,la ban-

de passante du bus PCI a également doublé,

passant de 33 à 66 MHz. Mais cette aug-

mentation,comparée à celle de la vitesse des

processeurs (de 33 MHz à 3 GHz),se révè-

le très insuffisante, en particulier si l’on consi-

dère les technologies d’entrées/sorties émer-

gentes comme l’Ethernet Gigabit et

l’IEEE 1394B (FireWire), qui peuvent mono-

poliser toute la bande passante disponible

du bus PCI avec un seul périphérique

connecté.Rappelons qu’outre la part dévo-

lue au protocole, la principale limitation

du PCI réside dans le partage de la bande

passante entre tous les périphériques

connectés sur le bus.Ainsi, l’architecture

parallèle du PCI commence à montrer ses

limites, en terme de bande passante, de

nombre de broches, de transfert de don-

nées temps réel, etc. Il ne peut répondre

aux besoins de la nouvelle génération de

périphériques comme la qualité de servi-

ce,la gestion d’alimentation et la virtualisa-

tion des entrées/sorties.

Pourtant,comme toute spécification qui

se respecte, celle du PCI a donné lieu à

des versions successives pour répondre

aux contraintes de bande passante. Des

dérivés du PCI comme les bus PCI-X et

AGP (Advanced Graphics Port) sont apparus

pour augmenter les fréquences de trans-

fert. L’AGP l’a d’ailleurs déjà remplacé

pour accroître les performances du cir-

cuit vidéo, tout en évitant de saturer la

bande passante que se partagent les

autres composants connectés sur le bus

du PC. On est ainsi passé de 132 Mo/s

(32 bits/33 MHz) avec le PCI à des

débits successifs de 266 Mo/s,533 Mo/s

et 1,04 Go/s avec respectivement

l’AGP 1X, 2X, 4X.

Moyennant une adaptation du protocole,le

PCI-X a permis d’augmenter la fréquence

du bus PCI en passant de 33 à 66, 100 ou

encore 133 MHz. Malheureusement, cette

augmentation de la bande passante s’ac-

compagne d’une réduction importante de

la distance sur laquelle les données peuvent

être acheminées et du nombre de connec-

teurs que les transmetteurs de bus peuvent

gérer. Par exemple, le PCI-X à 133 MHz

L’essentiel

Un nouveau bus baptisé

PCI Express est destiné à

unifier l’architecture des PC

de nouvelle génération.

Il a vocation à remplacer

l’actuel bus PCI ainsi que le

bus graphique AGP

Les différents débits de

cette interface seront lar-

gement supérieurs à ce qui

existe actuellement : de

250 Mo/s pour une version

1X à 8 Go/s pour une ver-

sion 32X.

Une rupture technologique

est à prévoir : les connec-

teurs PCI Express seront

incompatibles avec les

actuelles cartes PCI.

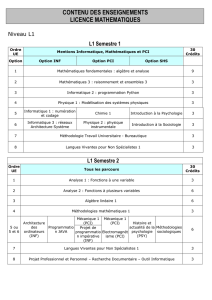

INFORMATIQUE INDUSTRIELLE

PCI Express : l

▼

Fortement soutenu par Intel, et les grands de l’informati

Express est destiné à devenir le bus de périphériques de

à moyen terme remplacer le bus PCI, qui après dix ans de

bande passante. En tant qu’interconnexion de type série

conventionnel qui est un bus parallèle. Évidemment,

public, finit tôt ou tard par arriver dans l’informatique ind

l’instrumentation sur PC, se prépare à ce nouveau stand

Le connecteur PCI Express X1 à 36 broches destiné à remplacer

l’actuel connecteur PCI sera nettement plus court que celui-ci,pour

un débit au moins double.

046_050_SOL 1/02/05 15:27 Page 46

47

MESURES 769 - NOVEMBRE 2004

S

olutions

n’offre plus qu’un seul slot sans répéteur.

Cela exige la division du bus PCI en plu-

sieurs segments,chacun nécessitant un bus

PCI-X complet entre le circuit de gestion et

chaque emplacement actif.Cette approche

est donc coûteuse à mettre en œuvre et

induit des contraintes au niveau du rou-

tage,du nombre de couches des cartes et

du brochage des composants. Le surcoût

induit peut uniquement se justifier lorsque

la conservation de la bande passante est

cruciale.C’est le cas pour les serveurs, par

exemple.

Un besoin de nouvelles

fonctionnalités

Les applications comme l’acquisition de

données,la génération de formes d’ondes,

le streaming audio et vidéo nécessitent une

bande passante garantie et des temps d’at-

tente déterministes.Les spécifications ori-

ginelles du PCI ne répondent pas à ces

besoins car ces applications n’étaient pas

déterminantes au moment du développe-

ment du bus.Les applications de transfert

isochrone de données, gourmandes en

bande passante,qui se développent aujour-

d’hui en vidéo et en audio, exigent la

nécessité de supporter aussi ce type de

transfert. Les transferts isochrones ont

notamment pour avantage,côté périphé-

rique, de nécessiter beaucoup moins de

mémoire tampon qu’il n’en faut actuelle-

ment en PCI pour résoudre les problèmes

de variation de bande passante.

D’autres besoins se dessinent : par

exemple, les périphériques de dernière

génération nécessitent de nouvelles fonc-

tionnalités en termes de gestion d’ali-

mentation pour permettre la mise hors

tension sélective de certaines parties du

système; cette considération est impor-

tante quand on voit que les PC modernes

nécessitent de plus en plus de puissance

électrique. Quant à la virtualisation des

entrées/sorties, il s’agit de pouvoir dispo-

ser de voies dynamiques pour permettre

Processeur

Bus AGP

Bus ATA

Bus

Bus processeur

Hublink ou autres

et slots PCI

Northbridge

Southbridge

Mémoire RAM

Disque dur

USB 1.1

Ethernet

E/S locales

Carte graphique

Architecture actuelle du PC

Chipset

Processeur

Bus ATA

Chipset

Bus

Bus processeur

et slots PCI

PCI Express

PCI Express

PCI Express

PCI Express

Northbridge

Southbridge

Mémoire RAM

Disque Dur

USB 2.0

Ethernet

Carte radio

Switch

E/S locales

Carte graphique

Architecture avec PCI Express

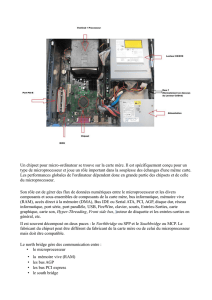

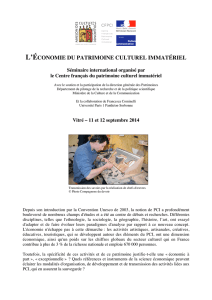

L’architecture du PC destinée à évoluer

L’architecture du PC repose depuis quelques années sur un certain nombre d’interconnexions différentes.Par exemple,les cartes graphiques sont

interfacées via le port AGP (Advanced Graphics Port),le Northbridge est connecté au Southbridge par une liaison appelée Hublink chez Intel

(l’ensemble Northbridge-Southbridge formant le chipset).PCI Express unifie l’ensemble en utilisant une architecture de bus commune.Il

devrait remplacer le bus AGP et réaliser la liaison entre le Southbridge et le Northbridge.Il devrait surtout fournir de nouveaux emplacements

pour les périphériques d’entrées/sorties.

le raz de marée est imminent…

tique bureautique (Dell, HP, IBM, Microsoft), PCI

des nouvelles générations de PC. Il devrait donc

de bons et loyaux services, montre ses limites en

e, PCI Express ne sera pas compatible avec le PCI

, ce qui se produit dans l’informatique grand

ndustrielle : National Instruments, spécialiste de

dard.

046_050_SOL 1/02/05 15:27 Page 47

le routage des données à travers des chemins

virtuels : des transferts peuvent ainsi être

effectués même si d’autres voies sont blo-

quées par des transactions prioritaires.

Un bus série commuté

Contrairement au bus PCI (qui est un bus

parallèle),le PCI Express fait appel à une com-

munication série commutée. Son architec-

ture est spécifiée sous forme de couches du

modèle OSI (voir figure).

Commençons par la couche la plus haute : la

couche logicielle de ce standard a été conçue

de façon à garantir la compatibilité logiciel-

le avec l’actuel PCI. Cette compatibilité

concerne deux aspects : le recensement auto-

matique de la carte et l’exécution des appli-

cations.Le premier aspect reprend les méca-

nismes standards définis dans la spécification

plug and play du PCI :il utilise le modèle d’ini-

tialisation très efficace de celui-ci,dans lequel

le système d’exploitation peut identifier tous

les matériels connectés sur le bus et allouer

en conséquence les ressources système,com-

me la mémoire,les interruptions, pour créer

un environnement système optimal.En pra-

tique,tous les systèmes d’exploitation seront

capables de démarrer les machines basées

sur PCI Express.

Le second aspect est plus impressionnant :

la compatibilité avec le modèle d’adressage

du PCI (architecture load/store à mémoire par-

tagée basée sur un adressage absolu) devrait

assurer que lors de la migration d’une carte

PCI vers son équivalent en PCI Express,toutes

les applications s’exécuteront sans aucune

modification logicielle. Enfin, les nouveaux

logiciels pourront aussi tirer avantage de cer-

taines des technologies avancées de PCI

Express, comme l’Advanced Switching, définie

comme une matrice de commutation de

paquets, qui cherche à cibler plus particu-

lièrement les applications de télécommuni-

cations.

Les couches logicielles vont générer des

requêtes de lecture et d’écriture transmises

aux périphériques d’entrées/sorties par la

couche transactionnelle. Celle-ci reçoit

les requêtes de lecture et d’écriture et crée

des trames de requêtes pour la transmis-

sion à la couche de liaison à l’aide d’un

protocole orienté paquets comme TCP/IP.

Comme celui-ci, certains paquets néces-

sitent un message de réponse (accusé de

réception). Cette couche reçoit donc des

trames de réponse en provenance de la

couche de liaison et les associe aux

requêtes logicielles originelles. Chaque

paquet a un identificateur unique qui per-

met de diriger les paquets de réponse vers

leurs initiateurs. Le format d’un paquet

offre un adressage de mémoire sur 32 bits

et un adressage étendu sur 64 bits.Chaque

paquet comporte également des attributs

comme no-snoop,relaxed ordering et priority qui

peuvent être utilisés pour optimiser leur

acheminement à travers le protocole de

niveau inférieur.

Le rôle d’une couche de liaison est d’as-

surer avec fiabilité la livraison d’un paquet

à travers la couche physique. La couche de

liaison est responsable de l’intégrité des

données.Elle ajoute donc à chaque paquet

de la couche transactionnelle des numéros

de séquence ainsi que des bits de contrôle

pour fiabiliser la transaction (CRC,Contrô-

le de Redondance Cyclique).Un protocole

de contrôle de flux,basé sur le principe de

crédits,garantit que les paquets sont trans-

mis uniquement lorsqu’une mémoire tam-

pon est disponible à l’autre extrémité.Cela

élimine les relances de paquets et la dégra-

dation de bande passante associée. La

couche de liaison relancera automatique-

ment l’envoi d’un paquet qui aura été signa-

lé comme corrompu.

La couche physique de base de l’interface

PCI Express se compose de deux canaux série

unidirectionnels, un canal émetteur et un

canal récepteur,l’ensemble formant une voie

de communication de base. Chaque canal

unidirectionnel est composé d’une paire dif-

férentielle de conducteurs véhiculant des

signaux basse tension. Le débit est de

2,5 Gbit/s dans chaque direction, soit envi-

ron 250 Mo/s en comptant les bits de

contrôle et d’initialisation,ce qui représen-

te à peu près deux fois la vitesse de transfert

48 MESURES 769 - NOVEMBRE 2004

S

olutions

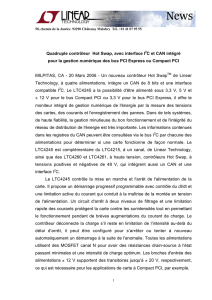

X16

X8

X4

X1

Différents formats de connecteurs selon les débits

Le bus PCI Express se décline en plusieurs versions,1X,2X,4X,8X,12X,16X et 32X associées chacune à un type de connecteurs.Le

connecteur 1X possède 36 broches et se destine à remplacer l’actuel slot PCI dans tous les PC bureautiques.Les connecteurs 4X et 8X pos-

sèdent respectivement 64 et 98 broches et se destinent à un usage sur serveurs :Le connecteur 16X possède 164 broches,mesure 89 mm de

long et a vocation à servir de port graphique en remplacement de l’AGP.

Connecteurs PCI

traditionnels

Connecteurs PCI Express X1

Connecteurs

PCI Express X16

(port graphique)

046_050_SOL 1/02/05 15:27 Page 48

du PCI classique. Cette vitesse de transmis-

sion de 1

ère

génération est censée augmenter

avec l’évolution de l’électronique pour dépas-

ser les 5 Gbit/s en deuxième génération et

venir flirter à plus long terme avec les

10 Gbit/s (la limite pour les signaux sur des

conducteurs en cuivre). Chaque octet est

transmis avec l’encodage 8B/10B. L’assem-

blage et le désassemblage des données sont

transparents pour les autres couches.Aucun

logiciel n’est impliqué dans cette transmis-

sion et surtout pas le système d’exploitation.

Ce mécanisme a été conçu dans la perspec-

tive des futures augmentations de la vitesse

de transfert et de l’évolution des techniques

d’encodage.Ces évolutions n’auront donc a

priori d’impact que sur la couche physique.

La bande passante du bus PCI Express peut

être étendue en ajoutant des voies de com-

munication de base, de façon à former des

voies multiples (en rappelant, qu’une voie

est formée de deux canaux en sens inverse,

qu’un canal est formé d’une paire de

conducteurs).Le bus PCI Express se décline

ainsi en plusieurs versions 1X, 2X, 4X, 8X,

12X,16X et 32X selon le nombre de voies de

base utilisées. La première génération per-

met d’obtenir des débits compris entre

250 Mo/s en version 1X et 8 Go/s en ver-

sion 32 voies (32x250 Mo/s),soit près de

4 fois le débit maximal des ports AGP 8X.

Avec un coût de fabrication similaire, le PCI

Express est donc amené à le remplacer pro-

gressivement.

Les connecteurs PCI Express sont incom-

patibles avec les anciens connecteurs PCI et

disposent d’une plus faible consommation

électrique.Une des caractéristiques intéres-

santes de ce bus est la possibilité de bran-

cher ou débrancher les composants à chaud,

c’est-à-dire sans éteindre le PC.Les connec-

teurs PCI Express sont reconnaissables grâce

à leurs petites dimensions et leur couleur

anthracite. Ils possèdent une taille variable

fonction des débits et des systèmes implé-

mentés.La couche physique fournit des lar-

geurs de voies de 1X, 2X, 4X, 8X, 16X et

32X sur lesquelles se répartissent les octets

à transmettre. Pour chacune de ces bandes

passantes,un type de connecteur est défini.

Le connecteur PCI Express de base sera le

connecteur 1X à 36 broches, destiné à tous

les PC bureautiques. Le connecteur 16X est

destiné à servir de port graphique et à rem-

placer celui de l’AGP.Par ailleurs,cette inter-

face a également vocation à supplanter la

technologie PC Card (ou encore PCMCIA)

sous la forme de connecteurs Express-

Card/54 (75x54x5 mm) et ExpressCard/34

(75x34x5 mm) plus compacts.

Des avantages pour la mesure et

l’automatisation

Ainsi, le PCI Express prendra peu à peu le

relais du bus PCI en apportant des amélio-

rations,sur plusieurs points importants.

49

MESURES 769 - NOVEMBRE 2004

S

olutions

Modèle plug-and-play du PCI

Modèle de logiciels et drivers PCI

Protocole basé paquets

Intégrité des données

Point à point,série, différentiel…

Augmentation

Couche physique

Couche de

Couche

Couche

Configuration

Indépendant

de l’OS

de l’OS

même principe que

TCP/IP

logicielle

transactionnelle

liaison de données

de la bande

passante

Un modèle en couches

PCI Express repose sur un modèle en couches indépendantes de type OSI.La couche transactionnelle comprend un protocole de communi-

cation orienté paquets comme TCP/IP.La couche physique est amenée à monter en débit sans impacter les couches supérieures.

046_050_SOL 1/02/05 15:27 Page 49

50 MESURES 769 - NOVEMBRE 2004

S

olutions

➔Hautes performances. Avec une ban-

de passante deux fois supérieure,en ver-

sion de base 1X, à celle du PCI et qui

croît linéairement à mesure que l’on

ajoute des voies de base, PCI Express

accélère considérablement les transferts

de données. Cette bande passante est

d’ailleurs disponible simultanément

dans les deux sens sur chaque canal. Le

débit initial de 2,5 Gbit/s devrait

atteindre progressivement 10 Gbit/s et

faire face ainsi à l’évolution des besoins

à long terme.

➔Simplification des entrées/sorties. Elle

découle directement de l’unification des bus

internes, accessibles ou non à l’utilisateur

(AGP, PCI, PCI-X et HubLink notamment).

Cette rationalisation devrait réduire la com-

plexité des conceptions et le coût de mise en

œuvre.

➔Architecture en couches. Ce format dis-

pose d’un modèle en couches indépendantes,

capable de s’adapter aux nouvelles technolo-

gies en préservant les investissements logi-

ciels.On peut ainsi s’attendre à une amélio-

ration des vitesses de transfert avec

conservation des couches logicielles hautes.

➔Cibler de nouvelles applications. Le

PCI Express offre de nouvelles possibilités

pour l’acquisition de données et le multi-

média grâce à des transferts de données

isochrones qui garantissent la qualité de

service et procure l’assurance de livrer les

données à temps grâce à des méthodes

déterministes.

➔Facilité d’utilisation. PCI Express va

considérablement simplifier la mise à niveau

des systèmes et l’ajout de nouveaux maté-

riels.Il offre l’insertion et l’extraction à chaud

des cartes (Hot Swap), une fonctionnalité

jusqu’ici réservée aux serveurs! Certes,com-

me celle-ci s’appuie sur des caractéristiques

spécifiques du système d’exploitation,il peut

y avoir un retard dans le lancement de nou-

veaux produits.

Durant ces quinze dernières années,pour

les systèmes de mesure et d’automatisa-

tion sur PC,le bus PCI s’est révélé être un

bus de prédilection. Il continuera à jouer

un rôle important dans les années à venir.

La transition vers PCI Express sera longue

et progressive : les nouveaux PC vont,petit

à petit,intégrer les deux types d’emplace-

ments PCI et PCI Express dans un rapport

qui tournera à l’avantage du PCI Express

au fur et à mesure de son adoption par le

marché.

Ajay V. Bhatt, architecte Desktop (Intel)

et Tim Fountain, Platform Manager

(National Instruments)

.

Paquet

Paquet

Horloge Horloge

Périphérique A Périphérique B

Couche physique de PCI Express

La couche physique de base 1X de PCI Express se compose de deux canaux unidirectionnels inverses à 250 Mo/s (compter 200 Mo/s de

débit utile dans chaque sens).

Multiplexage des voies de base

Plusieurs voies de base peuvent être ajoutées pour augmenter le débit et former une voie multiple :une liaison 4X est équivalente à 4 liai-

sons 1X,soit environ 4x250 Mo/s = 1 Go/s

Alors que les premières cartes au format

PCI Express ont fait leur apparition sur le mar-

ché purement informatique (cartes mères et

cartes graphiques) en septembre 2003, on

compte déjà deux cartes destinées au marché

industriel, toutes deux proposées par Natio-

nal Instruments. Il s’agit de la PCIe-GPIB, une

carte 1X d’interface GPIB et de la PCIe-1429,

une carte 4X d’acquisition d’images (à partir

de l’interface Camera Link).

La carte PCIe-GPIB n’a pour l’instant aucun

intérêt puisque les performances sont les

mêmes que celle de la carte PCI-GPIB. Elles

sont en effet limitées par la liaison GPIB

(1,5 Mo/s en mode IEEE 488.1 classique et

7,9 Mo/s en HS-488), il s’agit là de l’emploi

d’un marteau pour écraser une mouche ! En

revanche, la carte PCIe-1429 bénéficie pleine-

ment de la bande passante de PCI Express,

avec la possibilité de transmettre en continu

des images à la vitesse de 680 Mo/s (soit

l’équivalent du contenu d’un CD par

seconde !) ou encore 1 000 images par secon-

de à la résolution de 1 024x512 points. Les

performances sont donc largement supé-

rieures à celles des cartes d’acquisition

d’images interfacées en PCI traditionnel

(132 Mo/s théoriques en 33 MHz/32 bits, en

réalité 80 Mo/s ). Grâce à la compatibilité logi-

cielle inhérente entre PCI et PCI Express, ces

deux cartes peuvent être exploitées dans le

cadre d’applications existantes, sans modifi-

cations logicielles.

BB

Les premières cartes PCI Express pour

la mesure sont déjà là

046_050_SOL 1/02/05 15:27 Page 50

1

/

5

100%