Couche Jeu d`instruction

26/11/07 1

Couche Jeu d’Instruction

/ Instruction Set Architecture

(ISA)

L2 – I303

Séance 6

26/11/07 2

Architecture des ordinateurs

Introduction & Historique

Représentation des nombres

TDs

3h

Couche physique, circuits logiq.

Circuits séquentiels

Le chemin de donnée

Couche micro-architecture

Cycle d’exécution

Conclusion sur l’exécution

4h

Cours

CC

CC

Couche ISA

26/11/07 3

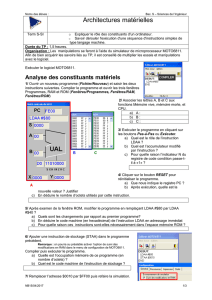

Notion de micro-architecture

Les choix d’organisation du chemin de donnée

forment ce que l’on appelle la microarchitecture

du processeur :

•Le CdD dispose de 2 ou 3 bus

•Le nombre de registres

•L’architecture dispose d’un pipeline

•Elle est superscalaire

•Son contrôle est microprogrammé ou cablé

•…

Le contrôle de l’exécution d’une instruction se fait

par une séquence de commandes appellées

–micro-commandes

–ou micro-instructions

26/11/07 4

Plan

1. Rôle et propriétés de la couche ISA

2. Organisation mémoire

3. Les registres de l’architecture

4. Types de données

5. Formats des instructions

26/11/07 5

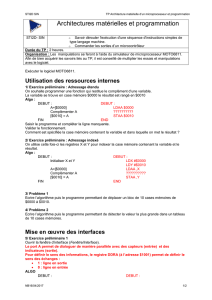

a. Le rôle de la couche ISA

Matériel

Couche ISA

Programme

en Fortran Programme en C

compilation compilation

Logiciel (software)

Matériel (hardware)

Exécution du programme ISA

Par matériel ou par microprogramme

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

1

/

59

100%