Examen Architecture des Ordinateurs I - 1ère Année Ingénieur

Telechargé par

mariemhajjem10

1

Devoir surveillé

Classe : 1ère année ingénieur Date : 02-12-2018

Matière : Architecture des ordinateurs I Durée : 1h15

NB. Aucun document ni machine (calculatrice, GSM) n’est autorisé.

Lisez bien l’énoncé jusqu’à la fin, soignez votre écriture et respectez ce qui est demandé de faire pour les

réponses.

Questions de cours (3,75 points)

Quelle est la différence entre :

1. La fréquence d’un processeur et la fréquence d’une mémoire.

La fréquence d’un processeur est proportionnelle à la fréquence horloge dont il va

suivre la cadence. Son inverse donne la durée d’un cycle horloge. Alors que la

fréquence d’une mémoire traduit l’inverse du temps nécessaire pour atteindre une

information, plus la fréquence est grande plus le temps est petit et donc la mémoire

plus rapide d’accès

2. Un processeur scalaire et un processeur vectoriel.

Un processeur scalaire traite une seule valeur à la fois alors qu’un processeur

vectoriel trait vecteur de valeurs tous en même temps

3. Un multi-processeurs et un multi-ordinateurs.

Un multiprocesseur c’est une architecture qui regroupe plusieurs processeurs dans

une même machine avec partage des ressources en particulier la mémoire centrale

alors qu’un multi-ordinateur c’est une architecture qui associe plusieurs ordinateurs

indépendants disposant de ressources privées via une infrastructure

d’interconnexion.

4. Le bus de données et le bus d’adresses.

Un bus de données sert à véhiculer les données de la mémoire vers le processeur et

vice versa (donc bidirectionnel) alors que le bus d’adresse n’achemine les adresses

que du processeur vers la mémoire et donc unidirectionnel. La largeur du bus

d’adresse donne une idée sur la capacité mémoire adressable alors que la largeur du

bus de donnée donne une idée sur la taille d’un mot mémoire.

5. L’adressage direct et l’adressage indirect.

Pour l’adressage direct nous disposons d’une adresse qui nous permet d’accéder à la

donnée en mémoire alors que pour l’adressage indirect nous disposons d’une

adresse mémoire qui nous permet d’accéder à une case mémoire contenant une

autre adresse qui nous mène à la donnée recherchée en mémoire.

2

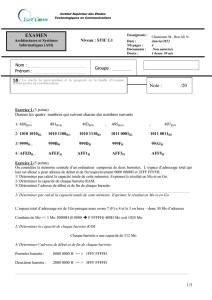

Exercice 1 (3,25 points)

1. Traduire le nombre décimal (-12,375) en nombre hexadécimal dans la norme

IEEE754 simple précision.

(-12,375) = (-1100,011)2= - 1,100011*23

Exposant : 3+127 = 130 = (10000010)2

Signe : 1

1 10000010 10001100000000000000000 = (C1460000)H

2. Donnez la valeur décimale du nombre représenté en hexadécimal par la valeur

C0B00000 dans chacune des cas suivantes :

a. Un nombre représenté dans la norme IEEE754 simple précision.

1 100 0000 1 011 0000 0000 0000 0000 0000

Signe : 1

Exposant : (10000001)2= 129 = 2 +127

Nombre = - 1,011*22 = (-101,1)2 = -5,5

b. Un nombre binaire signé.

-(230+223+221+220) = -(220*(210+23+21+20)) =

-(220*(210+23+21+20)) = -(1024+8+2+1)*220 = -1035*220 = -1035 Méga

c. Un nombre binaire non signé.

231+230+223+221+220 = 220*(211+210+23+21+20) = 220*(210*(21+20)+23+21+20) =

(1024*(3)+8+2+1)*220 = (3072+8+3) )*220 = 3083 Méga

3. Effectuer les opérations suivantes, en indiquant si le résultat est valide ou non

(0111011)2 + (ABCD)H

0000 0000 0011 1011 + 1010 1011 1100 1101 = 1010 1100 0000 1000 = (AC08)H

Résultat valide

(1422)H – (F010)H

1422 – F010 = 1422 + 0FF0 = 2412 = - DBEE

Résultat valide

Exercice 2 (4 points)

Soit un processeur qui tourne à une fréquence horloge de 2 GHz et qui exécute un

programme constitué d’un mélange de cinq types d'instructions :

3

1. Combien de cycles se programme prendra-t-il pour s’exécuter ?

(150000*1)+(45000*2)+(55000*2)+(20000*2)+(500*15)=

10000*(15+9+11+4)+5000+2500=(10000*39)+7500=397500 cycles

2. Quelle sera la durée totale d’exécution ?

(397500/2)*10-9 = 198750 ns

3. Calculez le CPI de ce programme.

Nombre de cycles / nombre d’instructions =

397500 /(150000+45000+55000+20000+500) =

397500 / (1000 * (150+100+20)+500) = 397500 / 270500 = 3975 / 2705 ~ 1,5

4. Calculez le MIPS de ce programme.

2 GHz / 1,5 presque égale à 1,3 milliard d’instruction par seconde

Exercice 3 (4 points)

Nous disposons d’un processeur doté d’un pipeline à 5 étages, chaque étage prenant

deux cycles. Dans ce qui suit, on négligera les surcoûts engendrés par le pipeline

1. Si une instruction entre dans le pipeline à l’instant i, à quel instant aura-t-elle fini

son exécution ?

Après (5*2) + i cycles

2. On considère un programme de n instructions. Calculez le temps nécessaire en

nombre de cycles pour son exécution.

Si n=1 5*2 cycles

Si n=2 5*2 + 2 cycles

Si n=3 5*2 + 4 cycles

Si n=4 5*2 + 6 cycles

Pour n 5*2 + (2*(n-1)) = 10 + 2n – 2 = 2n + 8 cycles

3. Quel est le CPI de ce programme sur ce processeur ?

(2n + 8)/n tend vers 2 quand n devient grand

4. Quel serait le CPI sur un processeur n’ayant pas de pipeline ?

10n / n = 10

Exercice 4 (5 points)

1. Coder en assembleur, l’itération suivante qui recherche l’indice et la valeur du

premier élément de la suite de Fibonacci de valeur inférieure à une valeur a

donnée :

4

i = 0;

x = 1;

y = 1;

while (x < a) // la variable a est supposée initialisée

{

z = x + y;

x = y;

y = z;

i = i + 1;

}

MOV i, 0

MOV x, 1

MOV y, 1

Boucle : MOV AL, x

CMP AL, a

JGE Quitter

ADD AL, y

MOV BL, y

MOV x, BL

MOV y, AL

INC i

Quitter :

2. Donner, en fonction de a, le nombre d’instructions qui seront exécutés.

3+ (Nombre d’itérations pour atteindre la valeur a)*8 + 3

3. Donner, en fonction de a et de tm, le nombre d’accès à la mémoire centrale que

ce soit pour chercher les données ou les instructions.

Pour les instructions (3 + (Nombre d’itérations avant d’atteindre la valeur a) * 8

+ 3) tm

Pour les données (3 + (Nombre d’itérations avant d’atteindre la valeur a)*7 + 2)

tm

((Nombre d’itérations avant d’atteindre la valeur a)*15 + 11) tm

- Bon travail -

1

/

4

100%