exercices - chapitre 2 - representation des informations

Page 1 / 5

Architecture des ordinateurs – UV 25971

Informatique Cycle A1

Regroupement 2 – Révisions

Année Universitaire 2004 – 2005

Centre Régional du CNAM de la Réunion

Durée : 2 heures

Rédacteur : Ivan KURZWEG - CNAM Réunion - ik[email protected]

Exercices du site d’aide au tutorat.

Page 2 / 5

EXERCICES - CHAPITRE 2 - REPRESENTATION DES

INFORMATIONS

Exercice 1 : Conversions entre base 2 ou 16 et 10

Convertir en base 10 les nombres suivants :

(0)2, (0)16, (1)2, (1)16, (10)2, (10)16, (12)16, (101)2, (BAFFE)16, (BAG)16

Convertir en bases 2 et 16 les nombres suivants (donnés en base 10) :

0, 1, 2, 3, 4, 8, 10, 15, 16, 31, 32, 128, 255

Exercice 2 : Conversions entre base 2 et 16.

Convertir (101011110000)2 en base 16.

Convertir (BAFFE)16 en base 2.

Exercice 3 : Entiers signés

Valeur absolue signée

Donnez la valeur absolue signée sur 8 bits des nombres décimaux suivants : 23, -23, -

48, -65

Complément à 2

Donnez la valeur en complément à 2sur 8 bits des nombres décimaux suivants : 23, -

23, -48, -65

Exercice 4 : Flottants

Convertissez les valeurs suivantes en IEEE754 Simple précision : 128, -32.75, 18.125, 0.0625

Quelles sont les valeurs des nombres suivant représentés en virgule flottant simple précision :

1011 1101 0100 0000 0000 0000 0000 0000

0101 0101 0110 0000 0000 0000 0000 0000

1100 0001 1111 0000 0000 0000 0000 0000

0011 1010 1000 0000 0000 0000 0000 0000

Page 3 / 5

EXERCICES - CHAPITRE 3 - DU PROBLEME AU LANGAGE

MACHINE

RAPPELS

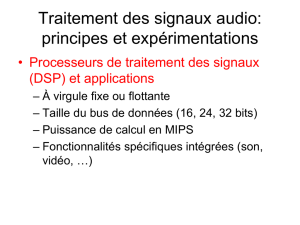

La machine admet des instructions sur 32 bits ou sur 16 bits.

Le format d’une instruction 32 bits est la suivante :

où

COP est le Code OPération codé sur 5 bits

m est le mode d’adressage codé sur 3 bits

Reg1et Reg2 codent un numéro de registre sur 4 bits (de 0000 à 1111)

champ2 est une valeur immédiate, une adresse mémoire ou un déplacement codé sur

16 bits

Les modes d’adressage; le champ m

La machine supporte les modes d’adressage mémoire suivants :

Immédiat

Opérande = valeur immédiate

m = 000

Direct

Opérande = [adresse]

m = 001

Relatif

Opérande = [[CO] + déplacement]

m = 010

Indirect

Opérande = [[adresse]]

m = 011

Basé

Opérande = [[RB] + déplacement]

m = 100

Indexé

Opérande = [[RIX] + déplacement]

m = 101

Pour ces valeurs de m comprises entre 0 et 5, le code opération travaille sur deux opérandes;

le premier est un registre dont le numéro est codé par le champ Reg1;

le deuxième est soit une valeur immédiate, soit une adresse déduite de Champ2 et m.

Les valeurs m = 110 et m = 111 sont utilisées pour les opérations sur des registres :

Page 4 / 5

110 : la valeur champ2 ainsi que celle du champ Reg2 sont non significatives; le Code

Opération travaille sur un seul opérande registre Reg1

111 : le code opération travaille sur deux registres Reg1 et Reg2.

Les valeurs des champs Reg

Les valeurs Reg(1ou2) = 0000 à 1011 codent les numéros de registres généraux R0 à R11.

Les autres valeurs sont réservées pour coder les autres registres du processeur. Ainsi :

Reg = 1100 registre CO

Reg = 1101 registre RB

Reg = 1110 registre RIX

Reg = 1111 registre PSW

Si le champ est mis à xxxx, cela signifie que le champ est invalide pour cette instruction.

Dans le cas particulier des opérations d’entrées-sorties, le champ Reg1 code un numéro de

port, pouvant aller de 0 à 15.

Les instructions

nb : par souci de clarté les codes opérations sont donnés non pas avec leur valeur numérique

mais en utilisant le mnémonique correspondant dans le langage d'assemblage.

La tableau ci-dessous donne la correspondance mnémonique – valeur du code binaire

Mnémonique

Code binaire

Mnémonique

Code binaire

LOAD

00000

JMPP

01101

STORE

00001

JMPO

01110

SWAP

00010

JMPN

01111

PUSH

00011

JMPC

10000

POP

00100

JMPZ

10001

ADD

00101

CALL

10010

NEG

00110

RET

10011

INCO

00111

EI

10100

AND

01000

DI

10101

OR

01001

OUT

10110

XOR

01010

IN

10111

NOT

01011

NOP

11000

JMP

01100

MUL

11001

Page 5 / 5

Exercice 1.Manipulation des modes d’adressages

Soient les registres et la mémoire adressable par mot à un instant t :

Adresse

Contenu

Registre

Contenu

100

a

RB

1

101

b

RIX

100

102

c

103

d

CO

50

200

300

201

304

Rsp

500

300

a

301

b

PSW

00000xxxxxxx

302

g

Soient les opérations suivantes; pour chacune d’elles, représentez l’évolution des registres du

processeur ainsi que celle de la mémoire et de la pile.

LOAD 001 0000 xxxx (100)10

LOAD 000 0000 xxxx (100)10

LOAD 011 0000 xxxx (200)10

PUSH 110 0000 xxxx

LOAD 100 0000 xxxx (200)10

NEG 110 0000 xxxx

ADD 000 0000 xxxx (304)10

PUSH 110 0000 xxxx

LOAD 101 0000 xxxx (1)10

POP 001 xxxx xxxx (202)10

POP 011 xxxx xxxx (201)10

Exercice 4. Langage d'assemblage et fonctionnement de l'assembleur

Ecrire en langage d'assemblage un petit programme permettant de calculer le périmètre d'un

polygone régulier formé de n cotés, chacun des cotés mesurant lg centimètres. Donnez le code

machine généré en fournissant la table des symboles construite.

1

/

5

100%