exercices d`architecture des ordinateurs

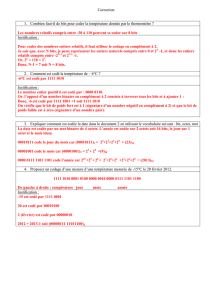

!"!#$%$!&'()*#$+%,!$,-#!'(!&'

.#(%/*,!-#&'

'

CHAPITRES*1&2*

01 $./2!#&%./'(*/&'(3*-,#!&'4*&!&'

567879'0:00:00:;'9<'=>68?@A1'

567879'BCDE'9<'F8<@879G'HI8J'9<'K9L@=>68?@A1'

$M<N97O87'0:00'00::'::::'0:::'00::'9<'=>68?@A'

;1 $.(*P!'!/'$.QRS!Q!/,'*';'

&I7'T'F8OJG'=M<<97'A9J'6M=@U9J'9<'6M?HA>?9<O'V';G'AM7JWI9'639JO'HMJJ8FA9G'=9J'<M?F79J'JI8N@<OJ'X'

:G'Y0G'Z0:G'Y0:G'ZECG'YECG'Z0;[G'Y0;[G'Z;::'

B1 *#%,+Q!,%\-!'4%/*%#!'

&I7'T'F8OJG'9]]96OI97'A@'JM??9'9<'F8<@879'X'0:00':0:02 + 00::'::002 9O'8<O97H7>O97'A9'7>JIAO@O'9<'>678OI79'

=>68?@A9G'9<'@78OK?>O8WI9'J8U<>9'9O'<M<'J8U<>91'%<=8WI97'=@<J'6K@WI9'6@J'J38A'^'@'=>FM7=9?9<O1'

'

$M?H@797'0:0:00::'9O'00::00::'9<'J8U<>'9O'<M<'J8U<>'

Q_?9'WI9JO8M<'HMI7'A@'JM??9'X'000':0:02 + 00::'::002

'

01 *SP!4#!'(!'4..S!'

&8?HA8]897'A39LH79JJ8M<'JI8N@<O9G'9<'IO8A8J@<O'A9J'OK>M7`?9J'=9'A3@AU`F79'=9'4MMA9'X'

𝐴.𝐵.𝐶+𝐴.𝐶.𝐷+𝐴.𝐶+𝐷'

C1 *SP!4#!'(!'4..S!'X'\-%/!'Q$'$S-&a!b'

&8?HA8]897'A39LH79JJ8M<'JI8N@<O9G'9<'IO8A8J@<O'A3@AUM78OK?9'=9'\I8<9'Q6$AIJc9^'X'

(1,2,3,5,7,11,13,17,19,23,29,31)!

D1 *SP!4#!'(!'4..S!'X'PS%,$+'

!<I?>797'OMIJ'A9J'UA8O6K9J'WI9'H9IO'H7>J9<O97'A39LH79JJ8M<'JI8N@<O9'X'

𝑆=𝐴!𝐵!𝐷+𝐵!𝐶!𝐷+𝐴!𝐶!𝐷'

R7MHMJ9d'I<9'9LH79JJ8M<'?M=8]8>9'WI8'JIHH78?9'OMIJ'69J'UA8O6K9J1'

E1 *SP!4#!'(!'4..S!'

Z'!67879'A9J'>WI@O8M<J'@JJM68>9J'V'I<'J6K>?@'

Z'MHHMJ>'=3I<9'JM??9'=9'?8<O97?9J'Ye'JM??9J'=9'OMIJ'A9J'@IO79J'

'

Y'>WI@O8M<'ef'gG'h'0;'

'

R7MIN97'@AU>F78WI9?9<O'iH@7'I<'6@A6IAj'WI9'A9'J6K>?@'JI8N@<O'9JO'I<'@==8O8M<<9I7'6M?HA9O'X'

'

[1 *SP!4#!'(!'4..S!'

#>>67879'A39LH79JJ8M<'JI8N@<O9G'I<8WI9?9<O'@N96'A3MH>7@O9I7'6M?HA9O'/*/('X'

".#i*G4j'

T1 $%#$-%,'$.Q4%/*,.%#!'X'&b/,+!&!'R*#',*4S!'(!'2!#%,!'

.<'JMIK@8O9'6M<69NM87'I<'6876I8O'6M?F8<@OM879'WI8'6@A6IA9'A@'N@A9I7'@FJMAI9'9<'F8<@879'HI7'JI7'C'F8OJ'LG^GdGO'=3I<'

<M?F79'6M=>'9<'6M?HA>?9<O'V';'JI7'C'F8OJG'@GFG6G=1'$@J'H@7O86IA897'X'J8'@F6=f0:::'iYTjG'@AM7J'L^dOf::::'i6@7'ZT'

<39JO'H@J'6M=@FA9'JI7'C'F8OJj'

(M<<97'A@'O@FA9'=9'N>78O>'=9'69'6876I8O'6M?F8<@OM879G'HI8J']MI7<87'A9J'>WI@O8M<J'=9'LG^GdGO'9<']M<6O8M<'=9'@GFG6G='

9<'A9J'J8?HA8]8@<O'@I'F9JM8<'V'A3@8=9'=9'O@FA9J'=9'a@<@IUK1'

g1 $%#$-%,'$.Q4%/*,.%#!'X'&b/,+!&!'k./$,%.//!SS!'

.<'JMIK@8O9'6M<69NM87'I<'6876I8O'6M?F8<@OM879'WI8'6M??@<=9'A3MIN97OI79'=3I<9'HM7O9'=9'l@7=8<'HIFA8WI9G'

MIN97O9'9<'K8N97'=9'0:K'V'0TK'9O'9<'>O>'=9'TK'V';:K1'S3K9I79'9JO'6M=>9'JI7'D'F8OJG'JMIJ']M7?9'=3I<'<M?F79'

9<O897'+'6M?H78J'9<O79':'9O';B'm'A@'J@8JM<'9JO'6M=>9'JMIJ']M7?9'=3I<'J8U<@A'&'i:fK8N97G'0f>O>j1'

$M<69NM87'I<'6876I8O'=38<O97]@69'PORTE(H[4..0], S : M)'O9A'WI9'Qf0'J8'9O'J9IA9?9<O'J8'X'

Y &'f':'9O'0:'n'+'n'0TG'MI'

Y &'f'0'9O'T'n'+'n';:'

.<'6M<69N7@'A9'6876I8O'=9']@oM<']M<6O8M<<9AA9G'9<'6M?F8<@<O'I<8WI9?9<O'X'

Y ;'6M?H@7@O9I7J'<M<'J8U<>J'JI7'D'F8OJ'

Y ;'?IAO8HA9L9I7J';'X0'MH>7@<O'JI7'=9J'FIJ'=9'D'F8OJ'

Y I<9'HM7O9'!,'V'=9IL'9<O7>9J'

0:1 $%#$-%,'$.Q4%/*,.%#!'X'$./$!R,%./'Q.(-S*%#!'

$M<JO7I879'I<'9<6M=9I7'=9'H78M78O>'V'T'9<O7>9J'@N96';'9<6M=9I7J'=9'H78M78O>'V'C'9<O7>9J1'S9J'6876I8OJ'M<O'

A38<O97]@69'X'

prioencoder4(e[3..0] : num[1..0], act)

prioencoder8(e[7..0] : num[2..0], act)

001 $%#$-%,'$.Q4%/*,.%#!'X'$./$!R,%./'Q.(-S*%#!'

$M<JO7I879'I<'?IAO8HA9L9I7'T'X0'@N96';'?IAO8HA9L9I7J'C'X0'9O'I<'?IAO8HA9L9I7';'X0'

0;1 $%#$-%,'$.Q4%/*,.%#!'X'$./$!R,%./'Q.(-S*%#!'

$M<JO7I879'I<'=>6M=9I7'B'X'T'@N96';'=>6M=9I7J';'X'C''

.<'IO8A8J97@'=9J'=>6M=9I7J'@N96'I<9'9<O7>9'!/'i9<@FA9j'

0B1 $%#$-%,'$.Q4%/*,.%#!'X'$./$!R,%./'Q.(-S*%#!'

$M<JO7I879'I<'6M?H@7@O9I7'<M<'J8U<>'=9'T'F8OJG'=38<O97]@69'X'

ucmp8(a[7..0], b[7..0] : sup, eq)

@N96';'6M?H@7@O9I7J'<M<'J8U<>J'=9'C'F8OJG'=38<O97]@69'X'

ucmp4(a[3..0], b[3..0] : sup, eq)

'

0C1 Q!Q.%#!&'

*JJM6897'C'?M=IA9J'?>?M879J'=9'Ca'?MOJ'=9'C'F8OJG'=38<O97]@69'mem4Kx4(addr[11..0], W, CE,

OE : data[3..0])'HMI7']M7?97'I<'?M=IA9'=9'0Ea'?MOJ'=9'C'F8OJ1'

'

CHAPITRES*3&4*

0D1 $%#$-%,'&!\-!/,%!S'X'$./$!R,%./'*2!$'P#*R+!'(3!,*,&'

$M<69NM87'I<'6876I8O'J>WI9<O89A'J^<6K7M<9'=38<O97]@69'croissant(rst, clk, a[1..0] : up)'O9A'WI9'

IHf0'J8'9O'J9IA9?9<O'J8'A@'N@A9I7'=9'@p011:q'@I']7M<O'=3KM7AMU9'9JO'HAIJ'U7@<=9'MI'>U@A9'i6M?H@7@8JM<'<M<'

J8U<>9j'V'A@'N@A9I7'=9'@p011:q'@I']7M<O'=3KM7AMU9'H7>6>=9<O'if'J8'@p011:q'67M8O'MI'79JO9'JO@FA9j1'

Y =9JJ8<97'A9'U7@HK9'=9'Q!*Sb'=9'69'6876I8O'

Y J^<OK>O8J97'A9'6876I8O'@N96'=9J'F@J6IA9J'('

0E1 $%#$-%,'&!\-!/,%!S'X'$./$!R,%./'k./$,%.//!SS!'

$M<69NM87''=9']@oM<']M<6O8M<<9AA9'I<'6876I8O'@<@AMUI9'@I'H7>6>=9<O'MH>7@<O'JI7'=9J'<M?F79J'=9'C'F8OJ'@N96'I<'

79U8JO79'C'F8OJ'9O'I<'6M?H@7@O9I7'<M<'J8U<>'JI7'C'F8OJ1'

0[1 $%#$-%,'&!\-!/,%!S'X'$./$!R,%./'*2!$'P#*R+!'(3!,*,&'

$M<69NM87'I<'6876I8O'=9'6M??@<=9'=9'6K@I=8`79'=38<O97]@69'X'

module chaudiere(rst, clk, chaud, froid : m)

]7M8=''f'0'JJ8'8A']@8O'?M8<J'=9'0Tr'm'6K@I='f'0'JJ8'8A']@8O'HAIJ'=9';;r'

S@'6K@I=8`79'=M8O'J9'?9OO79'9<'?@76K9'AM7JWI38A']@8O']7M8=G'9O'=M8O'J3@77_O97'AM7JWI38A']@8O'6K@I='

0T1 $%#$-%,'&!\-!/,%!S'X'*/*Sb&!'

.<'6M<J8=`79'A9'?M=IA9'&+(S'JI8N@<O'X'

module reverse(rst, h, f, c : s)

x := /tx*x + tx*/x;

x.clk = h;

x.rst = rst;

tx = c*x + f*c*/y + /c*/x*y;

y := dy ;

y.clk = h;

y.rst = rst;

dy = f*/y + /c*y + /f*/c*x;

s = y ;

end module

Y (9JJ8<97'A9'J6K>?@'=I'6876I8O'

Y !JOY69'I<'6876I8O'=9'QMM79'MI'=9'Q9@A^'s'

Y (9JJ8<97'A@'O@FA9'=9'O7@<J8O8M<J'

Y &8?HA8]897'A@'O@FA9'm'=9JJ8<97'A9'U7@HK9'J8?HA8]8>'

.<'<9'6K976K97@'H@J'V'J^<OK>O8J97'A9'6876I8O'J8?HA8]8>'

0g1 $%#$-%,'&!\-!/,%!S'X'P#*R+!'(3!,*,&'

.<'N9IO'7>@A8J97'I<9'J977I79'V'6M=9'J8?HA8]8>91'S9'6A@N897'9JO'6M?HMJ>'=9'B'OMI6K9J'X'tu3G't*3G't43'9O'I<9'A9='

J3@AAI?9'AM7JWI9'A@'FM<<9'J>WI9<69'@'>O>'O@H>9'@I'6A@N8971'S@'J>WI9<69'=3MIN97OI79'9JO'X'tu3G't43G't*31'S9'6876I8O'V'

7>@A8J97'@I7@'A38<O97]@69'X''

module serrure(rst, clk, dieze, a, b : ouvert)

.<']@8O'A9J'K^HMOK`J9'JI8N@<O9J'X''

Y''A3KM7AMU9'6Ac'9JO'JI]]8J@??9<O'7@H8=9'HMI7'<9'?@<WI97'@I6I<'>N><9?9<O'JI7'A9J'OMI6K9J'''

Y''A9'6A@N897'9JO'6M<oI'HMI7'WI3V'6K@WI9'8<JO@<OG'8A'^'@8O'd>7M'MI'I<9'OMI6K9'@HHI^>9G'l@?@8J''HAIJ89I7J'''

Y''9<O79';'@HHI8J'JI669JJ8]JG'A9J'O7M8J'OMI6K9J'JM<O'79Av6K>9J'''

S@'J>WI9<69'H7>68J9'=3>N><9?9<OJ'JI7'A9J'OMI6K9J'WI8'=>6A9<6K9'A3MIN97OI79'9JO'X'@HHI8'JI7'uG'@I6I<'@HHI8G'

@HHI8'JI7'4G'@I6I<'@HHI8G'@HHI8'JI7'*1',MIO'@HHI8'9<JI8O9'@77_O9'A3MIN97OI79'9O'6M??9<69'I<9'<MIN9AA9'

J>WI9<691''

Y''9LHA868O97'A9J'N96O9I7J'=9J'9<O7>9J'9O'=9J'JM7O89J'9O'=9JJ8<97'I<'U7@HK9'=9'QMM79'=9'69'J^JO`?9'''

Y''J8?HA8]897'>N9<OI9AA9?9<O'm'WI9AA9'9JO'A@'O@8AA9'=I'N96O9I7'=3>O@OJ's'''

Y''/!'R*&'J^<OK>O8J97'69'6876I8O'''

;:1 $%#$-%,'&!\-!/,%!S'X'&b/,+!&!'

.<'6M<J8=`79'A@'O@FA9'=9'O7@<J8O8M<J'=3I<'6876I8O'J^<6K7M<9'HI7'=9'O^H9'Q9@A^G'=39<O7>9J'*G'4'9O'=9'JM7O89'&'X'

A*

B*

état*

état*

S*

0*

:'

@'

@'

:'

0*

0'

@'

6'

0'

1*

:'

@'

F'

0'

1*

0'

@'

='

:'

0*

:'

F'

F'

0'

0*

0'

F'

='

:'

1*

:'

F'

@'

:'

1*

0'

F'

6'

0'

0*

:'

6'

@'

0'

0*

0'

6'

6'

:'

1*

:'

6'

F'

:'

1*

0'

6'

='

0'

0*

:'

='

F'

:'

0*

0'

='

='

0'

1*

:'

='

@'

0'

1*

0'

='

6'

:'

'

Y =M<<97'A@'O@8AA9'=9J'N96O9I7J'=39<O7>9JG'=3>O@OG'=9'JM7O89J'

Y J^<OK>O8J97'69'6876I8O'@N96'A9J'F@J6IA9J'=9'NMO79'6KM8LG'9O'=9JJ8<97'A9'6876I8O'6M779JHM<=@<O'

'

;01 $%#$-%,'&!\-!/,%!S'

(9JJ8<97'A9'U7@HK9'=9'Q..#!'=3I<'6876I8O'J>WI9<O89A'WI8'=>O96O9'A@'J>WI9<69'0G0'm'6M<69NM87'69'6876I8O'V'A3@8=9'

=3I<'79U8JO79'V'=>6@A@U9'=9';'F8OJ1'

,7@<J]M7?97'A9'U7@HK9'=9'Q..#!'9<'U7@HK9'=9'Q!*SbG'HI8J'6M<69NM87'A9'6876I8O'6M779JHM<=@<O1'

!<'J38<JH87@<O'=I'7>JIAO@O'MFO9<IG'H7M=I879'I<'6876I8O'=9'Q!*Sb'WI8'=>O96O9'A@'J>WI9<69'0G:G01'

6

6

7

7

8

8

9

9

10

10

1

/

10

100%