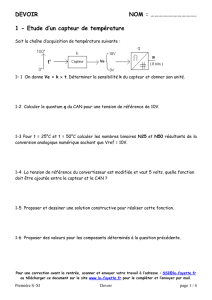

Conception d'un capteur de température, d'un récepteur

UNIVERSITÉ

DE

SHERBROOKE

Faculté

de

génie

Département

de

génie

électrique

et

de

génie

informatique

Conception

d'un

capteur

de

température,

d'un

récepteur

LVDS

et

d'un

générateur

de

charge

en

technologie

CMOS

0,18

pim

pour

un

scanner

TEP/TDM

Mémoire

de

maîtrise

Spécialité

:

génie

électrique

Mohamed

Walid

BEN

ATTOUCH

Jury

:

Réjean

FONTAINE

(directeur)

Jean-François

PRATTE

(co-directeur)

Cetin

AKTIK

(rapporteur)

Daniel

DALLE

(correcteur)

Sherbrooke (Québec)

Canada

Novembre

2011

Tt/-ouL*

Library

and

Archives

Canada

Published

Héritage

Branch

BibKothèque

et

Archives

Canada

Direction

du

Patrimoine

de

l'édition

395

Wellington

Street

Ottawa

ON

K1A

0N4

Canada

395,

rue

Wellington

Ottawa

ON

K1A0N4

Canada

Yourfite

Votre

référence

ISBN:

978-0-494-83723-8

Otir

file

Notre

référence

ISBN:

978-0-494-83723-8

NOTICE:

The

author

has

granted

a

non-

exclusive

license

allowing

Library

and

Archives

Canada

to

reproduce,

publish,

archive,

preserve,

conserve,

communicate

to

the

public

by

télécommunication

or

on

the

Internet,

loan,

distrbute

and

sell

theses

worldwide,

for

commercial

or

non-

commercial

purposes,

in

microform,

paper,

electronic

and/or

any

other

formats.

AVIS:

L'auteur

a

accordé

une

licence

non

exclusive

permettant

à

la

Bibliothèque

et

Archives

Canada de

reproduire,

publier,

archiver,

sauvegarder,

conserver,

transmettre

au

public

par

télécommunication

ou

par

l'Internet,

prêter,

distribuer

et

vendre

des

thèses

partout

dans

le

monde,

à

des

fins

commerciales

ou

autres,

sur

support

microforme,

papier,

électronique

et/ou

autres

formats.

The

author

retains

copyright

ownership

and

moral

rights

in

this

thesis.

Neither

the

thesis

nor

substantial

extracts

from

it

may

be

printed

or

otherwise

reproduced

without

the

author*s

permission.

L'auteur

conserve

la

propriété

du

droit

d'auteur

et

des

droits

moraux

qui

protégé

cette

thèse.

Ni

la

thèse

ni

des

extraits

substantiels

de

celle-ci

ne

doivent

être

imprimés

ou

autrement

reproduits sans

son

autorisation.

In

compliance

with

the

Canadian

Privacy

Act

some

supporting

forms

may

have

been

removed

from

this

thesis.

While

these

forms

may

be

included

in

the

document

page

count,

their

removal

does

not

represent

any

loss

of

content

from

the

thesis.

Conformément

à

la

loi

canadienne

sur

la

protection

de

la vie

privée,

quelques

formulaires

secondaires

ont

été

enlevés

de

cette

thèse.

Bien

que

ces

formulaires

aient

inclus

dans

la

pagination,

il

n'y

aura

aucun

contenu

manquant.

Canada

À

ma

mère,

à

mon

père,

à

ma

sœur

et

à

ma

fiancée

RÉSUMÉ

La

recherche

en

imagerie

moléculaire

repose

beaucoup

sur

les

performances

en

tomographie

d'émission

par

positrons

(TEP).

Les

avancées

technologiques

en

électronique

ont

permis

d'améliorer

la

qualité

de

l'image

fournie

par

les

scanners

TEP

et

d'en

augmenter

le

champ

d'application.

Le

scanner

LabPET

II,

en

développement

à

l'Université

de

Sherbrooke,

permettra

d'atteindre

des

résolutions

spatiales inégalées.

La

conception

de

ce

scanner

requiert

une

très

grande

densité

de

détecteurs

de

l'ordre

de

39

000

sur

un

anneau

de

15

cm

de

diamètre

par

12

cm

de

longueur

axiale.

D'autre

part,

l'Université

de

Sherbrooke

mène

également

des

travaux

en

tomodensitométrie

(TDM)

par

comptage

de

photons

individuels.

Ces

travaux

s'insèrent

dans

un

programme

de

recherche

menant

à

réduire

par

un

facteur

1,5

à

10

la

dose

de

rayon

X

par

rapport

aux

doses

actuelles

en

TDM.

Un

circuit

intégré

(ASIC)

a

été

développé

pour

supporter

les

performances

attendues

en

TEP

et

en

TDM.

Cependant,

la

très

grande densité

de

canaux

rend

inadéquate

la

vérification

externe,

sur

circuits

imprimés

(PCB),

des

fonctionnalités

des

64

canaux

d'acquisition

du

circuit

intégré

actuellement

en

conception.

Ainsi,

un

générateur

de

charge

électronique

a

été

conçu

et intégré

dans

l'ASIC

afin

de

pouvoir

vérifier

directement

sur

le

circuit

intégré

(On-Chip)

le

fonctionnement

de

la

chaine

d'acquisition.

D

permettra

aussi

de

faire

les

tests

pour

le

calcul

de

la

résolution

d'énergie

et

de

la

résolution

en

temps

intrinsèque.

La

communication

des

données

avec

l'ASIC

se

fait

par

une

ligne

différentielle

afin

de

maximiser

l'immunité

des

signaux

contre

le

bruit

et

d'assurer

la

vitesse

de

communication

voulue.

La

norme

Low-Voltage

Differential

Signaling

(LVDS)

a

été

choisie

pour

ce

type

de

communication.

En

effet,

trois

récepteurs

LVDS,

basse

consommation,

ont

été

conçus

et

intégrés

dans

l'ASIC

afin

de

recevoir

les

commandes

de

fonctionnement

de

l'ASIC

à

partir

d'une

matrice

de

portes

programmables

Field-Programmable

Gâte

Array

(FPGA)

et

de

communiquer

le

signal

d'horloge

aux

différents

blocs.

Pour

augmenter

la

fiabilité

du

traitement

effectué

par

l'électronique

frontale,

une

mesure

en

température

de

l'ASIC

est

nécessaire.

Un

capteur

de

température

basé

sur

la

boucle

à

délais

Delay-Locked

Loop

(DLL)

a

été

conçu

et

intégré.

En

effet,

la

mesure

de

la

température

de

l'ASIC

permet

d'intervenir

en

réalisant

une

compensation

sur

les

mesures

et

en

contrôlant

le

système

de

refroidissement

en

cas

de

sur-échauffement.

Mots-clés

:

Capteur

de

température,

Récepteur

LVDS,

Générateur

de

charge,

LabPET

II,

CMOS

0,18

pim,

Tomographie

d'émission

par

positrons

(TEP),

Tomodensitométrie

(TDM).

i

REMERCIEMENTS

En

préambule

à

ce

mémoire

de

maîtrise,

je

souhaite

adresser

mes

remerciements

les

plus

sincères

aux

personnes

qui

m'ont

apporté

leur

aide

et

qui

ont

contribué

à

l'élaboration

de

ce

mémoire

ainsi

qu'à

la

réussite

de

ces

formidables

années

universitaires.

Je

tiens

à

remercier

sincèrement

le

Pr.

Réjean

FONTAINE,

directeur

du

GRAMS

(Groupe

de

Recherche

en

Appareillage

Médical

de

Sherbrooke)

et

directeur

de

mon

projet

de

recherche.

Il

s'est

toujours

montré

à

l'écoute

et

très

disponible

tout

au

long

de

la

réalisation

de

ce

projet.

Il

a

été

une

source

d'inspiration,

fournit

aide

et

temps

sans

lesquels

ce

mémoire

n'aurait

jamais

vu

le

jour.

Mes

remerciements

s'adressent

également

à

Jean-François

PRATTE,

mon

co-directeur,

pour

sa

disponibilité,

sa

générosité

et

pour

ses

précieux

conseils.

Il

n'a

cessé

de

me

transmettre

son

savoir

faire,

son

expertise

dans

le

domaine

de

l'électronique

analogique

et

les

atouts

de

son

expérience

professionnelle.

Je

remercie

également

tous

les

membres

du

GRAMS,

particulièrement,

Mr.

Konin

Calliste

KOUA,

Mr

Sylvain

PANIER,

Mr

Louis

ARPIN,

Mr.

Mouadh

ABIDI,

Mr.

Moez

KANOUN,

pour

leur

aide,

leur

soutien

et

leurs

conseils

tout

le

long

de

la

réalisation

de

ce

projet.

Je

remercie

aussi

Caroline

PAULIN

pour

son

support

technique

et

pour

la

conception

des

cartes

de

tests.

J'adresse

mes

plus

sincères

remerciements

à

mes

parents

Mohamed

Lazhar

et

Dorra

et

à

ma

sœur

Rawia

pour

leur

contribution

et

leur

soutien

surtout

dans

les

périodes

les

plus

dures.

J'exprime

toute

ma

reconnaissance

à

ma

formidable

fiancée Sourour

qui

m'a

encouragé

et

supporté

pendant

toute

cette

période.

Et

je

n'oublie

pas

mon

meilleur

ami

Haithem,

pour

son

soutient

et

son

encouragement.

Enfin,

je

remercie

à

tous

mes

proches

et

amis,

qui

m'ont

toujours

soutenu

et

encouragé

au

cours

de

la

réalisation

de

ce

projet.

Merci

à

tous

et

à

toutes.

ii

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

1

/

130

100%