Prototype d`outil de modélisation graphique d`ingénierie syst

Sous-projet 1

strat´

egie de g´

en´

eration de tests sur la base de mod`

eles

environnementaux et de mod`

eles comportementaux

Prototype d’outil de mod´

elisation graphique

d’ing´

enierie syst`

eme en utilisant la g´

en´

eration

d’´

editeur avec PAPYRUS

Livrable n˚1.1

31 aoˆ

ut 2009

VETESS - Livrable n˚1.1

EVOLUTION DU DOCUMENT

Version Date Auteur Remarques

1.0 31/08/2009 LIFC - MIPS

CARACTERISTIQUES

Niveau de Diffusion Projet VETESS

Diffusion Public

2

Prototype d’outil de mod´elisation graphique SysML

Table des mati`eres

1 Introduction 7

1.1 Rappel de l’objectif du sous-projet SP1 . . . . . . . . . . . . 7

1.2 Situation au sein du sous-projet SP1 . . . . . . . . . . . . . . 7

1.3 Abr´eviations . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Positionnement dans l’´etat de l’art 9

2.1 Introduction au test `a partir de mod`eles . . . . . . . . . . . . 9

2.2 Langages de mod´elisation pour le test . . . . . . . . . . . . . 10

2.2.1 Sp´ecification alg´ebrique . . . . . . . . . . . . . . . . . 11

2.2.2 Alg`ebre de processus . . . . . . . . . . . . . . . . . . . 11

2.2.3 Structure de Kripke et logique temporelle . . . . . . . 11

2.2.4 Mod`ele de flots de donn´ees . . . . . . . . . . . . . . . 12

2.2.5 Mod´elisation par contrat . . . . . . . . . . . . . . . . . 12

2.2.6 Syst`eme de transitions ´etiquet´ees . . . . . . . . . . . . 12

2.2.7 Machine `a ´etats finie . . . . . . . . . . . . . . . . . . . 13

2.2.8 Synth`ese . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3 Langage de mod´elisation pour le projet VETESS . . . . . . . 14

2.3.1 Les notations UML et SysML . . . . . . . . . . . . . . 14

2.3.2 Le langage UML4MBT de Test Designer𝑇 𝑀 . . . . . . 15

2.3.3 Le langage SysML4MBT pour VETESS . . . . . . . . 15

2.4 Bilan et cas d’´etude illustratif . . . . . . . . . . . . . . . . . . 16

3 Diagramme de blocs SysML4MBT 17

3.1 Lesblocs ............................. 17

3.2 Les propri´et´es . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.3 Les op´erations . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4 Les associations . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.5 Lessignaux ............................ 21

3.6 Les sp´ecifications de flux . . . . . . . . . . . . . . . . . . . . . 22

3.7 Lesports ............................. 22

4 Diagramme interne de blocs SysML4MBT 23

4.1 Les propri´et´es . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.2 Lesports ............................. 24

4.3 Les connecteurs . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5 Diagramme d’´etats-transitions SysML4MBT 26

5.1 Les´etats.............................. 26

5.2 Les pseudo-´etats . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.1 ´

Etatinitial ........................ 27

5.2.2 Point de d´ecision . . . . . . . . . . . . . . . . . . . . . 28

5.2.3 Barre de fraction et barre de jonction . . . . . . . . . 29

3

VETESS - Livrable n˚1.1

5.2.4 ´

Etat historique et ´etat historique profond . . . . . . . 29

5.3 Les transitions . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.3.1 D´eclencheur . . . . . . . . . . . . . . . . . . . . . . . . 30

5.3.2 Garde ........................... 30

5.3.3 Effet............................ 30

5.4 Les actions onEntry/onExit . . . . . . . . . . . . . . . . . . . 34

6 Diagramme d’exigences SysML4MBT 34

6.1 Les exigences . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2 La tra¸cabilit´e des exigences . . . . . . . . . . . . . . . . . . . 35

6.3 Les Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.4 Les objectifs de test . . . . . . . . . . . . . . . . . . . . . . . 39

7 Mod´elisation SysML4MBT avec PAPYRUS 39

8 R´ecapitulatif du langage SysML4MBT 47

8.1 Diagramme de blocs . . . . . . . . . . . . . . . . . . . . . . . 47

8.2 Diagramme interne de blocs . . . . . . . . . . . . . . . . . . . 48

8.3 Diagramme d’´etats-transitions . . . . . . . . . . . . . . . . . . 49

8.4 Diagramme d’exigences . . . . . . . . . . . . . . . . . . . . . 50

9 Synth`ese 51

4

Prototype d’outil de mod´elisation graphique SysML

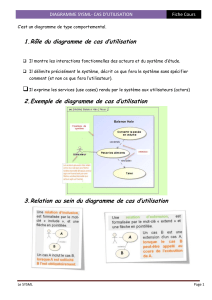

Table des figures

1 Repr´esentation d’un bloc SysML. . . . . . . . . . . . . . . . . 17

2𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Blocs SysML4MBT. . . . . . . . . . . . . . 17

3 Repr´esentation d’une ´enum´eration SysML. . . . . . . . . . . . 18

4𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Propri´et´es des blocs SysML. . . . . . . . . 18

5𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Op´erations des blocs SysML4MBT. . . . . 19

6 Associations du diagramme de blocs SysML4MBT. . . . . . . 20

7𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Diagramme de blocs SysML4MBT. . . . . 20

8 Signal du diagramme de blocs SysML4MBT. . . . . . . . . . 21

9𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Signaux SysML4MBT. . . . . . . . . . . . 21

10 Sp´ecification de flux du diagramme de blocs SysML4MBT. . 22

11 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Sp´ecification des flux SysML4MBT. . . . . 22

12 Propri´et´e du diagramme interne de blocs SysML4MBT. . . . 24

13 Types de port de SysML4MBT. . . . . . . . . . . . . . . . . . 25

14 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Diagramme interne SysML4MBT (propri´e-

t´es). ................................ 25

15 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Diagramme interne SysML4MBT. . . . . . 25

16 ´

Etats du diagramme d’´etats SysML4MBT. . . . . . . . . . . . 26

17 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 :´

Etats du diagramme d’´etats SysML4MBT. 27

18 Point de d´ecision du diagramme d’´etats SysML4MBT. . . . . 28

19 Barres de fraction et de jonction SysML4MBT. . . . . . . . . 29

20 ´

Etat historique SysML4MBT. . . . . . . . . . . . . . . . . . . 29

21 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Diagramme d’´etats SysML4MBT. . . . . . 31

22 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Mod´elisation dynamique du controller. . . 32

23 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Mod´elisation dynamique HighLight. . . . . 33

24 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Mod´elisation dynamique HeadLight. . . . . 33

25 Diagramme d’exigences SysML4MBT. . . . . . . . . . . . . . 34

26 𝐹 𝑟𝑜𝑛𝑡𝐿𝑖𝑔ℎ𝑡𝑖𝑛𝑔𝑠 : Diagramme d’exigences. . . . . . . . . . . . 35

27 Lien satisfy simple SysML4MBT. . . . . . . . . . . . . . . . . 36

28 Liens satisfy parall`eles SysML4MBT. . . . . . . . . . . . . . . 36

29 Liens satisfy multiples SysML4MBT. . . . . . . . . . . . . . . 37

30 ´

Equivalence des liens satisfy multiples SysML4MBT. . . . . . 37

31 Diagramme d’exigences de l’exemple des feux. . . . . . . . . . 38

32 Exemple avanc´e de diagramme d’exigences SysML4MBT. . . 39

33 Diagramme de blocs r´ealis´e avec PAPYRUS . . . . . . . . . . 40

34 Enum´erations (dans un diagramme de blocs) r´ealis´ees avec

PAPYRUS ............................ 41

35 Signaux et sp´ecifications de flux (dans un diagramme de blocs)

r´ealis´es avec PAPYRUS . . . . . . . . . . . . . . . . . . . . . 42

36 Diagramme interne de blocs r´ealis´e avec PAPYRUS . . . . . 43

37 Diagramme ´etats-transitions r´ealis´e avec PAPYRUS . . . . . 44

38 Diagramme ´etats-transitions r´ealis´e avec PAPYRUS . . . . . 45

39 Diagramme d’exigences r´ealis´e avec PAPYRUS . . . . . . . . 46

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

1

/

56

100%