Document

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

MINISTERE DE L4ENSEINEMENT SUPERIEUR

ET DE LA RECHERCHE SCIENTIFIQUE

UNIVERSITE DE BATNA

FACULTE DES SCIENCES DE L’INGENIEUR

MEMOIRE

Présenté au

DEPARTEMENT D’ELECTRONIQUE

Pour l’obtention du diplôme de

MAGISTER EN MICROELECTRONIQUE

Option : IC Design

Par

Samia KHALDI

Ingénieur, institut d’Electronique-Université de Batna

Intitulé

Conception et Layout d’un CNA pour un

capteur de pression intelligent

Devant le jury constitué de :

Dr. HOBAR Farida

Dr. BOUGUECHAL Nour-Eddine

Dr. MANK Otto

Prof. Université de Constantine

Prof. Université de Batna

Prof. Université de Berlin

M.C. Université de Batna

M.C. Université de Batna

C.C. Université de Batna

Dr. DIBI Zohir

Dr. HAFDHI Zoubida

Mr. BENHAYA Abdelhamid

Président

Rapporteur

Rapporteur

Examinateur

Examinateur

Examinateur

A la mémoire de mon père.

Remerciements

Je tiens tout d’abord à remercier le professeur Nour Eddine Bouguechal, le doyen

de la faculté des sciences de l’ingénieur à l’université de Batna. Pour son travail

d’encadrement, ses conseils, et pour qu’il m’a été permis de savoir de tout prés la conception

réelle dans l’industrie électronique. Je lui suis très reconnaissant pour ses qualités rares tant

au niveau humain que scientifique que j’ai pu entrevoir dans les déplacements que nous avons

été amenés à effectuer ensemble. Je lui dois les remerciements les plus sincères.

Je tiens particulièrement à remercier Mr. Otto Manck, directeur général de la société

MAZ, et professeur à l’université technique de Berlin en Allemagne, où nous avons effectué une

grande partie de ce travaille, pour la confiance qu’il m’a témoignée en m’accueillant dans son

équipe à Berlin et pour ce captivant sujet de recherche proposé.

J'adresse tous mes remerciements à Monsieur Mr. R. Arnold, docteur à l’université

technique de Berlin, pour m’avoir accueilli au sein de son équipe de recherche et sa patiente

relecture du manuscrit et ses qualités pédagogiques que j’apprécie beaucoup. Son soutient

constant sur les plans scientifiques et humains aura été une aide particulièrement précieuse.

Mes vifs remerciements à Mme. Farida Hobar, professeur à l’université de

Constantine, pour avoir accepté de présider le jury et a bien voulu prendre le temps de

s’intéresser au sujet du présent mémoire.

De même à Mr. Zohir Dibi, docteur et chef du département d’électronique de

l’université de Batna, pour sont aide, ces conseils ont été d’une grande valeur, aussi m’a t-il

honoré de faire partie du jury.

Je tiens à remercier vivement Mme. Zoubida Hafdhi, docteur et chargé de cours à

l’institut d’électronique à l’université de Batna,, pour m’avoir honoré par sa présence au jury.

Je remercie également Mr Benhaya Abdelhamid, chargé de cours à l’institut

d’électronique, pour son aide, pour l’honneur qu’il me fait en figurant dans la composition du

jury.

Un grand merci à ma petite famille, à ma grande famille, à toutes mes aimées et à tous

les collèges du laboratoire de l’électronique avancée à Batna pour leur dynamique.

Je ne pourrai jamais trouver les mots justes pour exprimer mes sentiments pour ma mère.

Je veux la remercier pour son soutien, ses sacrifices, la patience, la volonté et la persévérance

qui m’ont permis de mener ce travail.

Mm Samia KHALDI

Sommaire

Introduction

1. L’ASIC de correction de pression

2. Description fonctionnelle de l’ASIC

3. Les spécifications de convertisseur Numérique/Analogique

4. Organisation du travaille

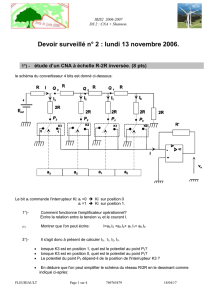

Chapitre I : Spécifications et limites de conversion du CNA

I.1 Définitions

I.2 Caractéristiques principales

I.2.1) Résolution

I.2.2) Précision

I.3 Spécifications

I.3.1 Erreur de gain

I.3.2 Erreur d’offset

I.3.3 Les erreurs de Linéarité

I.3.4 Monotonicité

I.3.5 Temps d'établissement

I.3.6 Bande passante

I.4 Les limites de conversions

I.4.1 La génération de référence

a) Echelle résistive RCNA

a.1) Les disparités des composants

a.2) Les erreurs d’établissement

a.3) Les erreurs d’interrupteur

b) Somme de courants ICNA

b.1) Les disparités de courant

b.2) L’impédance finie de sortie

b.3) Erreur de commutation (Glitch)

c) Echelle capacitive CNA

c.1) Les disparités des capacités

c.2) La tension dépendant de condensateur

I.4.2 Les erreurs de circuit E/BMOS

a) L’injection de charge

b) Le couplage capacitif d’horloge

I.4.3 Les composantes d’erreur aléatoire

a) Le bruit thermique (KT/C)

b) Le bruit de scintillement (1/f) « Flicker »

Conclusion

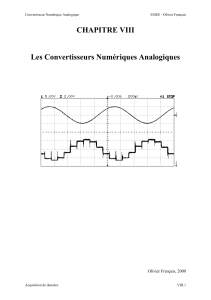

Chapitre II : Les Architectures des CNAs

II.1 CNA Parallel (Flash)

II.1.1 CNA à série de résistance

II.1.2 Le CNA flash à réseau de capacités

II.1.3 CNA flash à somme de courants

II.2 Les CNAs sériel

1

2

2

3

3

5

5

7

7

7

7

7

8

8

10

10

10

11

11

11

11

13

13

14

14

15

15

16

16

16

17

17

19

20

20

21

22

23

24

24

27

28

i

II.2.1 CNA cyclique

II.2.2 CNA Pipeline

II.3 Conclusion

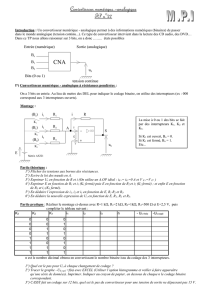

Chapitre III : Conception et Simulation

III.1 CNA à amplificateur de charge binaire pondéré

Dimensionnement de la valeur de capacité de contre Réaction

III.2 CNA à Amplificateur de Réseau de charge en T

Dimensionnement de la valeur de capacité d’atténuation

III.3 Schéma synoptique

III.4 La logique de commande RUNDAC

III.5 CNA à amplificateur de réseau de charge en T

III.5.1 Conception et simulation

III.5.2 Considération pratiques et interprétations

a) La vitesse et la linéarité

b) L’injection de charge

c) La consommation électrique

d) L’intégrateur

III.6 La tension de référence VREF

III.7 L’échantillonneur bloqueur

a) Le suiveur

b) L’injection de charge

III.8 La tension du mode commun

Considération pratiques et interprétations

III.9 Le circuit de polarisation en courant IBias

a) Conception et simulation

b) Considération pratiques et interprétations

III.10 Résultat de simulation de circuit totale

Chapitre IV Masque (Layout) de CNA

4.1 Considération de Layout

a) Technique d’appariement

b) Considération du bruit

4.2 Floor-planning

4.3 La partie analogique

4.2.1 Le réseau de capacités

4.2.2 Les amplificateurs et le circuit VCM

a) L’intégrateur

b) Les résistances et le condensateur du circuit VCM

4.2.3 Réseau d’interrupteurs

4.2.4 L’échantillonneur bloqueur

4.2.5 Circuit de polarisation en courant IBias

4.4 La partie numérique

4.5 Le layout du CNA

Conclusion

29

30

32

33

34

34

35

36

38

38

40

41

41

43

43

44

45

45

48

48

49

51

51

52

52

53

55

56

61

62

62

63

64

66

66

70

70

71

71

72

73

75

76

77

ii

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

1

/

104

100%