Exploitation de la simulation du circuit MS_CPL

*Exploitation de la simulation du circuit MS/CPL :

Les circuits utilisés sont les suivant :

4 inverseurs ( 74LS04 )

1 adder ( 74LS283 )

2 multiplexeurs ( 74LS153 )

1 porte NOR ( 74LS27 )

1 porte ET ( 74LS08 )

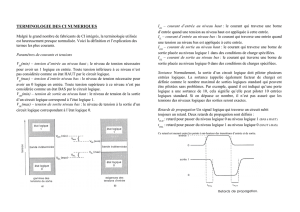

Les temps de propagations donnés par le constructeur sont les

suivants :

- Pour l’inverseur : TPLH = 9 ns

TPHL = 10 ns

- Pour l’adder : TPLH = 15 ns

TPHL = 15 ns

- Pour le multiplexeur : TPLH = 10 ns

TPHL = 17 ns

- Pour la porte NOR : TPLH = 10 ns

TPHL = 10 ns

- Pour la porte ET : TPLH = 8 ns

TPHL = 10 ns

Après simulation, on obtient les résultats suivants :

La sortie B(7 : 0) est en retard par rapport à l’entrée A(7 : 0) avec les

temps suivants :

Pour des nombres positifs :

TPHL = 17 ns

TPLH = 10 ns

Page 38

Justification :

TPHL = TPHL du 74LS153 = 10 ns

TPLH = TPLH du 74LS153

= 10 ns

Ces deux retards sont ceux correspondants aux nombres positifs qui sont

appliqués à l’entrée A(7 : 0). Etant positifs ces nombres ne passent pas

dans la première partie du circuit, mais seulement dans les multiplexeurs.

On a donc en sortie uniquement les retards des multiplexeurs qui sont prit

en compte. C’est pour cela que les retards correspondent exactement à

ceux des multiplexeurs.

Pour des nombres négatifs :

TPHL = 42 ns

TPLH = 35 ns

Justification :

TPHL = TPHL du 74LS153 + TPHL du 74LS04 + TPLH du 74LS283

= 10 ns + 9 ns + 15 ns

= 34 ns

Les temps correspondent presque avec ceux donnés par le constructeur.

Page 39

1

/

2

100%