Aucun titre de diapositive

2

Sommaire

Introduction

Chapitre 1 - Caractéristiques électriques d’une porte logique TTL-standard

1-1- Tensions

1-2- Courants

1-2-1- Courant de sortie (sortie «totem pôle»)

1-2-2- Courant d’entrée

1-3- Connexion d’une sortie à une entrée

1-4- Connexion d’une sortie à plusieurs entrées

1-5- Sortance (fan-out)

1-6- Connexion des sorties

1-7- Cas des entrées non utilisées

1-8- Découplage de la source d’alimentation

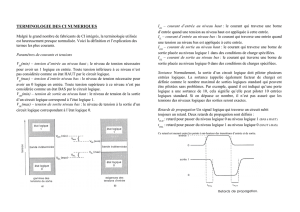

1-9- Durées de propagation

1-10- Fréquence maximale d’utilisation

1-11- Schéma interne des portes logiques

1-12- Consommation électrique

3

Sommaire

Chapitre 2- Porte à entrées «&Trigger de Schmitt&»

Chapitre 3- Sortie en configuration «&buffer&»

Chapitre 4- Sortie en configuration «&collecteur ouvert&»

Chapitre 5- Sortie en configuration «&3 états&»

Chapitre 6- Autres familles TTL-5 volts

Conclusion

Bibliographie

4

Introduction

Les circuits intégrés de la famille TTL-Standard sont à l’échelle de

l’électronique, très anciens (milieu des années 60).

Et pourtant, ils sont encore commercialisés !

J’ai en ma possession de vieux data book de Texas Instruments

datant de 1972.

On y retrouve les fonctions habituelles (porte, multiplexeur, bascule,

compteur, registre, buffer …).

Certaines références sont maintenant caduques, mais la plupart

existent encore (qui ne connaît pas la première de la série, le 7400

?).

Je vous propose, dans ce qui suit, d’en savoir un peu plus.

5

Chapitre 1 - Caractéristiques électriques d’une

porte logique TTL-standard

1-1- Tensions

H = High-level = niveau logique «1» (en logique positive)

L = Low-level = niveau logique «0» (en logique positive)

I = Input

O = Output

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

1

/

62

100%