CIRCUITS INTÉGRÉS NUMÉRIQUES

CIRCUITS

INTÉGRÉS

NUMÉRIQUES

Introduction

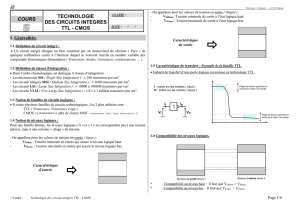

Systèmes linéaires

les variables d'entrées et sorties sont continues et

s'expriment analytiquement,

les relations entrées/sorties sont définies par des

équations différentielles ou par leurs transformées.

Systèmes numériques

les variables sont discontinues et

ces fonctions de transfert ne s'expriment plus en

termes de temps ou de fréquences, mais sous forme

de tables ou de relations booléennes.

Les images des grandeurs physiques récupérées

en sortie des capteurs sont analogiques.

Longtemps, elles ont été récupérées et traitées

comme telles et elles le restent encore dans

certains systèmes (télévision pour quelques

temps encore).

Ce type de signal pose de nombreux problèmes :

conception des systèmes délicate,

sensibilité au bruit,

stockage d'information moins performant….

Électronique linéaire

Électronique numérique

Permet d'atténuer nombre de ces inconvénients :

les valeurs des signaux étant quantifiées, ils sont

moins sensibles au bruit (transmissions),

le stockage d'informations est plus simple et plus fiable,

on peut réaliser ou programmer des séquences

évoluées complexes et

l'intégration des composants est bien plus grande

qu'en analogique (on n'a plus à intégrer des

inductances ou des capacités notamment…)

Fonctions logiques élémentaires

Ces circuits effectuent sur ces signaux les

opérations de base de l'algèbre de Boole:

opérations ET, OU et Complément.

A ces opérations de base on ajoute en général

les fonctions incluant une inversion :

NAND , NOR ainsi que le OU Exclusif XOR .

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%