Cours Bus SPI - Bac pro SN

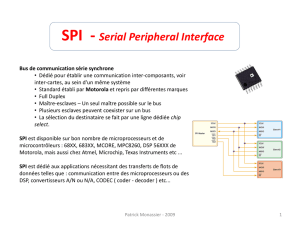

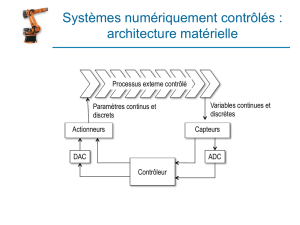

Bus de communication série synchrone

• Dédié pour établir une communication inter-composants, voir

inter-cartes, au sein d'un même système

• Standard établi par Motorola et repris par différentes marques

• Full Duplex

• Maître-esclaves – Un seul maître possible sur le bus

• Plusieurs esclaves peuvent coexister sur un bus

• La sélection du destinataire se fait par une ligne dédiée chip

select.

SPI est disponible sur bon nombre de microprocesseurs et de

microcontrôleurs : 68XX, 683XX, MCORE, MPC8260, DSP 56XXX de

Motorola, mais aussi chez Atmel, Microchip, Texas Instruments etc ...

SPI est dédié aux applications nécessitant des transferts de flots de

données telles que : communication entre des microprocesseurs ou des

DSP, convertisseurs A/N ou N/A, CODEC ( coder - decoder ) etc...

SPI - Serial Peripheral Interface

1 BAC PRO SEN

Le bus SPI contient 4 signaux logiques :

• SCLK — (généré par le maître)

• MOSI — (généré par le maître)

• MISO — (généré par l'esclave)

• SS — Slave Select, Actif à l'état bas (généré par le maître)

Il existe d'autres noms qui sont souvent utilisés :

• SCK — Horloge (généré par le maître)

• SDI,DI,SI — Serial Data IN

• SDO,DO,SO — Serial Data OUT

• nCS, CS, nSS, STE — SS

Dans le cas de la convention de nommage SDI/SDO, le SDO du maître

doit-être relié au SDI de l'esclave et vice-versa. Pour éviter les

confusions au moment du câblage, il est donc souvent recommandé

d'utiliser les dénominations MISO-MOSI qui évitent une certaine

ambiguïté.

Les signaux :

2

Le bus SPI est une liaison série synchrone qui opère en mode "full duplex" - émission /

réception simultanée

La méthode d'accès et du type maître / esclave et c'est toujours le maître qui a

l'initiative des échanges : quand le maître sélectionne l'esclave et génère l'horloge, les

données sont échangées dans les deux directions, simultanément.

Le maître ne tient pas compte de la donnée reçue dans le cas d'un échange "écriture

seule" ou alors il envoie un octet sans importance ( 0xFF ) dans le cas d'un échange

"lecture seule" ;

La communication avec un esclave de type CODEC par exemple (coder-decoder), permet

d'exploiter pleinement les capacités du bus SPI, avec un flot de données bidirectionnel.

Le maître génère l'horloge et sélectionne l'esclave avec qui il veut communiquer.

L'esclave répond aux requêtes du maître.

A chaque coup d'horloge le maître et l'esclave s'échangent un bit.

Après huit coups d'horloges le maître a transmis un octet à l'esclave et vice-versa.

La vitesse de l'horloge est réglée selon des caractéristiques propres aux périphériques.

Principes :

3

Il est possible de choisir le type d’horloge grâce à une combinaison de 2 bits dans le registre

SPCON : le bit noté CPOL (Clock POLarity) et le bit noté CPHA (Clock PHAse).

• CPOL détermine le niveau logique de la ligne SCK au repos.

• CPHA détermine le front sur lequel la donnée est modifiée et le front sur lequel la donnée

va être lue.

Les signaux :

Les modes 0 et 3 sont identiques en

transmission, seule change l'état de la

ligne d'horloge au repos .

C'est pour cette raison que de

nombreux périphériques peuvent être

capables de dialoguer soit en mode 0

et 3, soit en mode 1 et 2.

Mode

CPOL

CPHA

O

0

0

1

0

1

2

1

0

3

1

1

Chronogramme des différentes configurations d'horloge

4

En mode maître, la vitesse de transmission est sélectionnée par 3 bits du registre SPCON (Serial

Peripheral CONtrol register): SPR2, SPR1 et SPR0.

La fréquence d’horloge est choisie parmi 7 fréquences obtenues par division de la fréquence de

fonctionnement du microcontrôleur.

SPR2 : SPR1 :

SPR2

Fréquence de

la SPI

000

Fμc/2

001

Fμc/4

010

Fμc/8

011

Fμc/16

100

Fμc/32

101

Fμc/64

110

Fμc/128

Pour le SPI il est possible de

trouver certains composants au

delà de 20 Mbits

5

La vitesse :

Le chaînage SPI :

Certains composants SPI sont conçus pour être chaînés,

simplifiant ainsi les connexions entre composants, en réduisant

le nombre de lignes SS nécessaires.

6

6

7

7

1

/

7

100%