Réseau Intégré Tridimensionnel Architecture et Implantation

Réseau Intégré Tridimensionnel

Architecture et Implantation

Hamed (Abbas) Sheibanyrad

Frédéric Pétrot

Premières Journées du Projet SEmba

Plan

•L’Intégration Tridimensionnelle

•Distribution de l’Horloge et le Paradigme GALS

•Réseau-sur-Puce Asynchrone

•La Contribution de la Troisième Dimension

•Nouvelles Idées

•Conclusion

2

Premières Journées du Projet SEmba - Abbas Sheibanyrad

23/10/2009

Evolution de la Technologie !

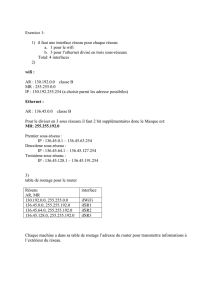

Système-sur-Carte Système-sur-Puce

•Evolution de la technologie de fabrication

–Intégration de système des milliards de transistors dans

une seule puce

–Des centaines et même des milliers de composants

– Rôle clé de l’infrastructure de communication

– Passage à l’échelle

IP0

IP10

IP1

IP2

IP3

IP4

IP5

IP6

IP7 IP8

IP9

IP11

IP12

IP13

IP14

IP15

Shared BUS

BUS Controller

Router

IP0

Router

IP3

Router

IP12

Router

IP15

Router

IP1

Router

IP2

Router

IP13

Router

IP14

Router

IP4

Router

IP7

Router

IP8

Router

IP11

Router

IP5

Router

IP6

Router

IP9

Router

IP10

3

Premières Journées du Projet SEmba - Abbas Sheibanyrad

23/10/2009

… mais, la terre devient chère !

•Comme la terre devient de plus en plus chère, il y a une tendance de

construire vers le haut plutôt que l’horizon

–Augmentation de la densité

–Réduction de la longueur et du nombre des longs chemins

•Dimensions Limités du Substrat de Silicium (Die)

–Contraintes du Rendement (Yield)

et la Performance

4

Premières Journées du Projet SEmba - Abbas Sheibanyrad

23/10/2009

Pourquoi pas l’Intégration 3D des Siliciums ?

pas de Connexions Externes

Grand Substrat

Possibilité d’Intégrer

Différents Substrat

avec Différentes

Technologies dans la

Même Package

5

Premières Journées du Projet SEmba - Abbas Sheibanyrad

23/10/2009

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

1

/

23

100%