+ V - CINaM

11/09/01 Cours d ’électronique analogique 1

11/09/01 Cours d ’électronique analogique 2

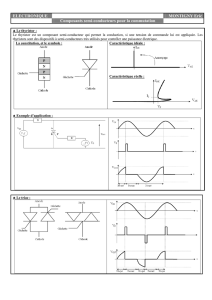

SEMICONDUCTEURS

XV – L’amplificateur opérationnel parfait

+

-

AV

2

Z

ediff

Z

e

Z

sortie

•Gain en tension infini

•Impédance d’entrée différentielle, Z

ediff

infinie

•Impédance d’entrée Z

e

infinie

•Impédance de sortie nulle

~ 10

3

à10

6

~ 10

4

à10

9

~ 10

4

à10

9

≤

≤≤

≤100 Ω

11/09/01 Cours d ’électronique analogique 3

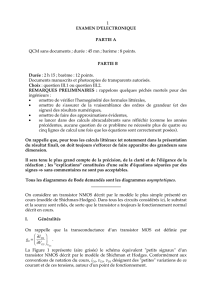

REACTION ET CONTRE REACTION

I – BOUCLE OUVERTE - BOUCLE FERMEE

Amplificateur

Gain : A

Considérons un amplificateur A

amplificateur A

Source

qui est attaqué par une source S

source S

Charge

un circuit de charge C

circuit de charge C :

et qui attaque lui-même

S

1

S

2

Ce montage est dit en boucle ouverte

S

1

est le signal en entrée de l’amplificateur

S

2

est le signal en sortie de l’amplificateur

12

S.AS =

==

=

11/09/01 Cours d ’électronique analogique 4

REACTION ET CONTRE REACTION

I – BOUCLE OUVERTE - BOUCLE FERMEE (suite)

Mais, …

le gain de l’amplificateur peut varier à cause de différents paramètres extérieurs

•Température,

•Dérive des tensions d’alimentation,

•Changement d’un composant,

•Etc…

Il faut donc trouver le moyen de stabiliser le gain de l’amplificateur. Le moyen le plus

simple consiste à réinjecter une partie du signal de sortie, S2, en entrée de

l’amplificateur (c’est à dire sommer cette partie de S2 avec S1).

On dit alors que l’on opère une réaction de la sortie sur l’entrée

une réaction de la sortie sur l’entrée (on parle aussi

d’asservissement de l’entrée par la sortie).

Le système est dit alors en boucle fermée

11/09/01 Cours d ’électronique analogique 5

REACTION ET CONTRE REACTION

I – BOUCLE OUVERTE - BOUCLE FERMEE (suite)

Deux cas se présentent alors :

1. Le signal réinjecté à l’entrée est en phase avec le signal d’entrée, on parle alors

de réaction positive

réaction positive (que l’on désignera tout simplement par réaction). Nous

verrons par la suite que la réaction est à l’origine de la conception des

oscillateurs.

2. Le signal réinjecté à l’entrée est en opposition de phase avec le signal d’entrée,

on parle alors de réaction négative

réaction négative (que l’on désignera plus simplement par

contre-réaction

Amplificateur

Gain : A

Source S Charge C

S

2

=A.S

1

S

1

=S - S

r

B

S

r

= B.S

2

S

2

B est le gain de la chaîne de

contre-réaction.

B comme A peut être réel ou

complexe

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

1

/

60

100%