CNA CAN - Academie pro

IUT de Nancy-Brabois Fabrice Sincère http://perso.orange.fr/fabrice.sincere page 1/4

M

ODULE D

’E

LECTRONIQUE

C

ONVERSION

N

UMERIQUE

→

→→

→

A

NALOGIQUE

C

ONVERSION

A

NALOGIQUE

→

→→

→

N

UMERIQUE

A- Etude théorique

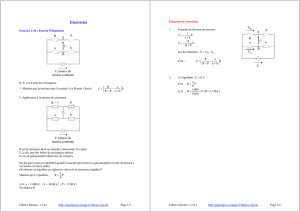

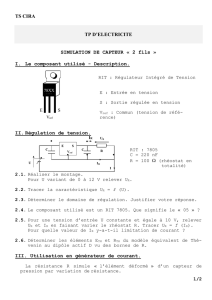

A-1- CNA 3 bits à réseau de résistances pondérées

L’interrupteur K

i

est associé au bit a

i

.

Si K

i

est ouvert : a

i

= 0 (niveau logique bas).

Si K

i

est fermé : a

i

= 1(niveau logique haut).

Déterminer la relation qui lie la tension de

sortie au nombre binaire d’entrée :

N = (a

2

a

1

a

0

)

2

.

En déduire la tension de pleine échelle et la

résolution (ou quantum).

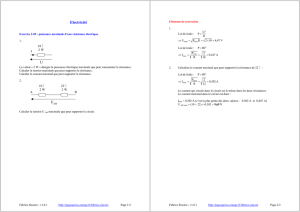

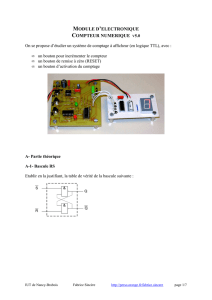

A-2- Etude d’un CNA 8 bits intégré : le DAC 08C

Le DAC 08C réalise la conversion d’un nombre binaire de 8 bits (A

1

...A

8

)

2

en un courant i

S

tel que :

+++++++−= 256

A

128

A

64

A

32

A

16

A

8

A

4

A

2

A

R

V

i

8765

4

3

21

14

REF

S

5

A

1

6

A

2

A

37

A

48

14

15

13

DAC 08C

9

A

5

10

A

6

A

711

A

812

1

2

4

163

C

-V

CC

= -15V

R

14

R

15

V

REF

=+5 V

i

S

+V

CC

= +15V

+

-

+

R

2R

R

R/2

K

0

K

2

K

1

E

u

S

IUT de Nancy-Brabois Fabrice Sincère http://perso.orange.fr/fabrice.sincere page 2/4

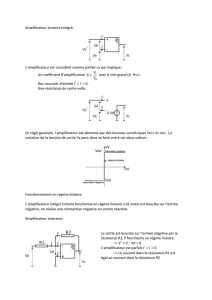

Pour obtenir en sortie une tension, on ajoute le montage suivant :

Montrer que u

S

= qN avec :

256

V

R

R

q

REF

14

=

En déduire la tension de pleine échelle.

Quelle est la résolution numérique (en %) ?

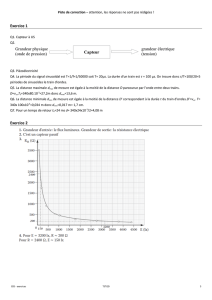

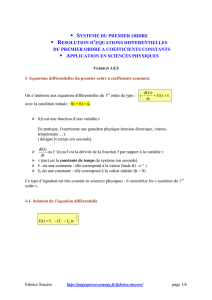

A-3-CAN « flash » 2 bits

Les AO fonctionnent en comparateur :

Si ε > 0 V : en sortie tension de niveau logique 1.

Si ε < 0 V : en sortie tension de niveau logique 0.

La tension d’entrée doit être comprise entre 0 V et V

REF

.

Tracer (et justifier) la caractéristique de transfert N = (a

1

a

0

)

2

en fonction de u

E

:

+

-

+

R

u

S

i

S

4

N

u

E

V

REF

11

10

01

00 0

&

&

&

&

+

+

-

+

+

-

+

+

-

R

R

R

R

V

REF

u

E

(t)

s

2

s

1

s

0

a

0

a

1

IUT de Nancy-Brabois Fabrice Sincère http://perso.orange.fr/fabrice.sincere page 3/4

B- Etude expérimentale

B-1- CNA 3 bits à réseau de résistances pondérées

Câbler le montage avec E = 2,50 V, R = 4,7 kΩ.

L’AO est alimenté en ± 15 V.

Pour chaque valeur de N mesurer la tension de sortie.

En déduire la tension de pleine échelle et la résolution.

Comparer avec la théorie.

B-2- Etude d’un CNA 8 bits intégré : le DAC 08C

Câbler le montage avec V

REF

= 5,00 V, R = R

14

= R

15

= 4,7 kΩ et C = 10 nF.

L’AO est alimenté en ± 15 V.

Mesurer la tension de sortie pour les entrées suivantes :

N = 00000000, 00000001, 00000010, 00000100, 00001000, 00010000, 00100000, 01000000,

10000000 et 11111111.

Remarque : à l’entrée, le niveau logique

• 1 correspond au potentiel +V

CC

= +15 V (ou entrée « en l’air »).

• 0 correspond au potentiel 0 V (masse).

En déduire la tension de pleine échelle et la résolution.

Comparer avec la théorie.

Ne pas décâbler !

B-3-CAN « flash » 2 bits

Câbler le montage suivant avec V

REF

= 5,00 V, R = 4,7 kΩ et diodes Zener 3,3 V:

&

&

&

&

+

+

-

+

+

-

+

+

-

R

R

R

R

V

REF

=5V u

E

(t)

s

2

s

1

s

0

a

0

a

1

IUT de Nancy-Brabois Fabrice Sincère http://perso.orange.fr/fabrice.sincere page 4/4

Les AO sont alimentés en +5 V et – 15 V.

Le circuit logique 7400 est alimenté en +5V et 0V.

La tension d’entrée est une tension continue réglable de 0 à 5 V (fournie par un GBF).

Tracer la caractéristique de transfert N = (a

1

a

0

)

2

en fonction de u

E

.

Ne pas décâbler !

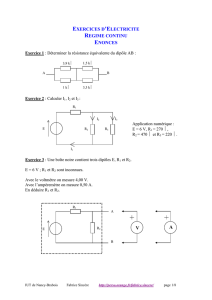

B-4-Association CNA/CAN

Relier la sortie a

1

du CAN à l’entrée A

1

du DAC 08C.

Relier la sortie a

0

du CAN à l’entrée A

2

du DAC 08C.

Les entrées A

3

à A

8

sont au niveau logique 0.

En utilisant le mode XY de l’oscilloscope, tracer la caractéristique de transfert u

S

(u

E

).

Comparer à la théorie.

Pour différentes formes de la tension d’entrée observer l’allure de la tension de sortie

(chronogrammes).

Justifier l’appellation de tension « numérique » en sortie.

C- Conclusion

a0

a1

A

2

A

1

u

E

(t)

0/5 V u

S

(t)

liaison

numérique

1

/

4

100%