tp_Portes logiques_2014-2015

SEN TP2 Tp logique

Les portes logiques

1. Introduction aux opérateurs logiques

a. Schéma

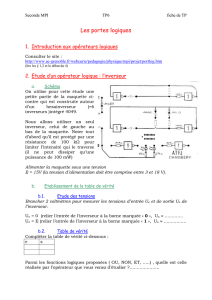

On utilise pour cette étude une petite partie de la maquette ci-contre qui est

construite autour d’un circuit intégré 4049.

Nous allons utiliser un seul inverseur, celui de gauche au bas de la

maquette. Noter tout d’abord qu’il est protégé par une résistance de 100 kΩ

pour limiter l’intensité qui le traverse (il ne peut dissiper qu’une puissance

de 100 mW)

Alimenter la maquette sous une tension de E = 5V.

b. Etablissement de la table de vérité

b.1. Etude des tensions

Brancher 2 voltmètres pour mesurer les tensions d’entrée U

e

et de sortie U

s

de

l’inverseur.

U

e

= 0 (relier l’entrée de l’inverseur à la borne marquée « 0 », U

s

≈ ………….

U

e

= E (relier l’entrée de l’inverseur à la borne marquée « 1 », U

s

≈ …………….

b.2. Table de vérité

Compléter la table de vérité ci-dessous :

e s

1/4

SEN TP2 Tp logique

c. Caractéristique de transfert

c.1. Manipulation

Rajouter un générateur de tension réglable (attention aux compatibilités de

bornes avec l’alimentation précédente)

Faire vérifier le montage avant de mettre le générateur de tension réglable

sous tension.

Faire varier la tension d’entrée U

e

de 0,2 V en 0,2 V et de 0 à E (ne pas

dépasser E = 5 V) et relever la tension de sortie U

s

. Faire un tableau de

relevés.

c.2. Résultats

Noter les résultats dans un tableau et tracer la courbe U

s

= f (U

e

)

Pour quelle valeur de U

e

y a-t-il basculement ?

2. Synthèse

a. Travail demandé :

Faire une synthèse sur la porte logique :

2/4

1

4

3

2

5

7

6

14

11

12

13

10

8

9

0 V

V+

SEN TP2 Tp logique

3. Portes logiques à 2 entrées

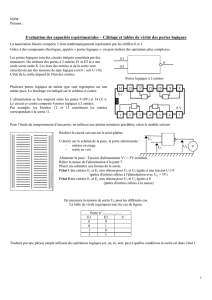

a. Présentation des portes logiques de la série CMOS 4000

Les portes logiques de la famille CMOS 4000 sont des circuits intégrés à 14 pattes.

Un petit ergot permet un repérage correct des pattes.

Dans toute la famille CMOS 4000, l’alimentation

doit être comprise entre 3 et 18 V.

Cette alimentation se fait toujours entre les pattes

7 (0V) et 14 (Vcc).

Le circuit ci-contre comporte 4 portes logiques à 2

entrées et une sortie.

Par exemple, les pattes 12 et 13 constituent les entrées correspondantes à la sortie

11.

b. Objectif

Vous disposez de plusieurs circuits intégrés qui sont des portes logiques

appartenant à la famille CMOS 4000.

Ils portent les numéros :

4001 4011 4070 4071 4081

L’objectif de la séance est d’établir leur table de vérité à l’aide du montage décrit ci-

dessous et d’identifier chaque porte en comparant sa table de vérité obtenue avec la

base de données de la 1

ère

séance.

c. Montage

Le montage sera alimenté sous une tension de +15 V.

On réservera sur la plaquette d’essai P60 une ligne +15 V et une ligne 0 V.

Chaque entrée sera protégée par une résistance de 100 kΩ.

L’état de la sortie sera donné par une diode protégée par une résistance de 470 Ω.

Exemple pour la porte : entrées 13 et 12 - sortie 11

3/4

Ligne + 5 V

1

4

3

2

5

7

6

14

11

12

13

10

8

9

0 V

V+

100 k Ω

100 k Ω

Ligne 0 V

E2

E1

S

SEN TP2 Tp logique

Faire vérifier impérativement le montage avant de le mettre sous tension (au

risque de détériorer le circuit intégré).

Ensuite, il suffira de changer seulement le circuit intégré, en prenant la précaution

de couper l’alimentation lors du changement.

d. Travail écrit demandé

Donner la table de vérité expérimentale pour chaque circuit intégré en indiquant

son numéro.

En déduire la fonction logique associée et donner le symbole de la porte

correspondante.

E1 E2 S E1 E2 S E1 E2 S

E1 E2 S E1 E2 S

e. Documents possibles à consulter

http://mpimichelet.free.fr/portes-logiques.html

f. Travail demandé :

Faire une phrase synthèse sur chaque porte logique :

4001 :_____________________________________________________________________________

4011 :_____________________________________________________________________________

4070 :_____________________________________________________________________________

4071 :_____________________________________________________________________________

4081 :_____________________________________________________________________________

4/4

1

/

4

100%