Les portes logiques

M.P.I. Seconde

LES PORTES LOGIQUES

I- Initiation à l’électronique numérique

1°) La logique binaire

Prenons l’exemple d’un interrupteur. Il possède deux états de fonctionnement: ouvert (on lui affecte l’état 0) et

fermé (l’état 1). La variable (0 ou 1) caractérise alors l’état de l’interrupteur.

Y a-t-il passage du courant dans le circuit contenant cet interrupteur ?

•Oui, si la variable caractérisant son état est 1.

•Non, si la variable caractérisant son état est 0.

Utilisons les variables (0 et 1) pour analyser la situation suivante : nous souhaitons obtenir de la peinture verte en

mélangeant de la peinture bleue et de la peinture jaune. Quatre cas peuvent se présenter :

−nous n’avons ni bleu ni jaune : ça ne peut pas marcher ;

−nous avons du bleu mais pas de jaune : ça ne peut pas marcher ;

−nous avons du jaune mais pas de bleu : ça ne peut pas marcher ;

−nous avons du bleu et du jaune : ça marche !

On rassemble ces résultats dans le tableau ci-contre appelé table de vérité.

0 et 1 portent le nom de variables logiques, au même titre que les signes + et -, ET est un opérateur. Puisqu’il

agit sur des variables logiques, on le nomme opérateur logique.

Bleu Jaune Bleu ET Jaune

(Vert)

0 0 0 ET 0 = 0

101 ET 0 = 0

010 ET 1 = 0

111 ET 1 = 1

2°) Les portes logiques

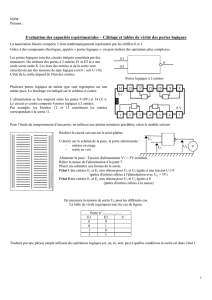

a) Notions de niveau logique et de fonction logique •En électronique, on utilise des circuits intégrés appelés portes logiques. La plupart des portes présente

deux entrées et une sortie.

Pour ces composants, la tension d’entrée , comme celle de sortie, peut

appartenir à deux domaines de valeurs définissant un état (ou niveau) haut ou bas, état

électrique pour lequel on fait correspondre une variable logique 0 ou 1 :

état bas pour Ve < VL (on lui fait correspondre la valeur logique : 0)

état haut pour Ve > VH (on lui fait correspondre la valeur logique : 1)

Rq. : Pour une tension d’entrée, ou de sortie, comprise entre VL et VH, aucune

valeur logique n’est affectée à la variable, l’état de la porte logique n’est pas clairement défini.

•Considérons un circuit logique à deux entrées E1 et E2. Chaque entrée peut prendre les valeurs logiques 0

et 1. L’état de chaque entrée constitue une variable logique. L’état de la sortie S du circuit constitue une

fonction logique des états des entrées.

b) Les familles de circuits intégrés logiques

Les portes logiques ne sont pas technologiquement identiques. Deux grandes familles sont à retenir :

•La famille Transistor Transistor Logic (TTL), de part son ancienneté, est sans doute la plus riche en

fonctions logiques . Cependant elle se caractérise par une tension d’alimentation qui doit être régulée à

5 V. La série standard « 74xx », la plus ancienne, est moins utilisée de nos jours, car sa consommation

est élevée (10 mW par porte), et le circuit intégré est sensible aux perturbations engendrées par le

basculement des portes.

•La famille Complementary Metal-Oxyde Semi-conductor (CMOS), plus récente, possède moins de

fonctions. La tension d’alimentation peut prendre une valeur comprise entre 3 V et 18 V et autorise une

large gamme de tensions d’entrée (variant de 0 V à 18 V suivant la tension d’alimentation). Ces

circuits intégrés sont moins sensibles aux tensions parasites pouvant créer des perturbations, leur

consommation est plus faible (10 nW par porte), mais ils sont très sensibles aux charges

électrostatiques environnantes.

- 1 -

V

DD

état haut = "1"

état bas = "0"

v

e

(V)

V

L

V

H

t

doc. 1

II- Les fonctions logiques de base

1°) Fonction à une seule variable

Avec une seule variable d’entrée E et deux valeurs logiques (0 ou 1), 4 fonctions sont réalisables :

1) E S 2) E S

0 0 0 1

1 1 1 0

La première table de vérité est la fonction identité ou OUI; elle est symbolisée par le premier schéma ci-dessous :

La deuxième table de vérité est la fonction inversion logique ou NON; elle est symbolisée par le deuxième

schéma ci-dessous :

2°) Fonction à deux variables

a) Fonction ET (C.I. AND , CMOS 4081 et TTL 7408)

E1E2S

0 0 0

0 1 0

1 0 0

1 1 1

Conclusion :

Il faut que E1 ET E2 soient à l’état 1

pour que S soit à l’état 1

sinon, S est à l’état 0.

b) Fonction ET - NON (C.I. NAND , CMOS 4011 et TTL 7400)

E1E2S

0 0 1

0 1 1

1 0 1

1 1 0

c) Fonction OU (C.I. OR , CMOS 4071 et TTL 7432)

E1E2S

0 0 0

0 1 1

1 0 1

1 1 1

Conclusion :

Il faut que E1 OU E2 soient à l’état 1

pour que S soit à l’état 1

sinon, S est à l’état 0.

d) Fonction OU - NON (C.I. NOR , CMOS 4001 et TTL 7402)

E1E2S

0 0 1

0 1 0

1 0 0

1 1 0

e) Fonction OU exclusif (C.I. XOR , CMOS 4077 et TTL 74263)

E1E2S

0 0 0

0 1 1

1 0 1

1 1 0

Conclusion :

Il faut que E1 OU Exclusif E2 soient

à l’état 1 (mais pas les deux)

pour que S soit à l’état 1

sinon, S est à l’état 0.

- 2 -

E1 E 1

SS

E1

&

S

E2

E1

&

S

E2

E1

≥ 1

S

E2

E1

≥ 1

S

E2

E1

= 1

S

E2

1

/

2

100%