Thèse de Doctorat Dans ce qui suit, je vais présenter mes travaux

Thèse de Doctorat

Dans ce qui suit, je vais présenter mes travaux de Thèse de Doctorat en mettant le point,

tout d’abord, sur la présentation du sujet, ensuite je vais donner un résumé des travaux qui ont

été élaborés ainsi que des travaux en cours.

Présentation du sujet :

Mon sujet de recherche en thèse porte sur l’implémentation sur FPGA de systèmes

universels à réseaux de neurones basés sur le mode impulsionnel. Les grandes lignes de ce

sujet comportent :

Une étude bibliographique portant sur le fondement biologique des réseaux de

neurones impulsionnels et la description de l’environnement de conception des circuits

dédiés.

La conception du réseau de neurones impulsionnels en Feed-Forward.

La conception du réseau de neurones impulsionnels avec apprentissage sur puce.

Le choix des exemples d'illustration et présentation des résultats de simulation et de

synthèse sur FPGA.

Travaux élaborés :

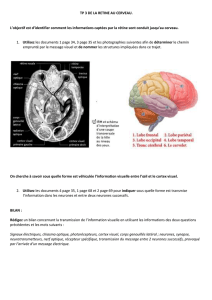

J’ai débuté mes travaux de thèse par une étude bibliographique sur le fondement

biologique des réseaux de neurones impulsionnels. Ensuite, j’ai présenté un aperçu sur les

modèles généraux des réseaux de neurones artificiels et j’ai décrit l'environnement de travail

et les étapes de conception de ce type de réseaux.

La conception du réseau de neurones impulsionnels en Feed-Forward est entamée en

second lieu. J’ai détaillé la conception des différents blocs du réseau (synapse, fonction

d'activation, codage de données, etc,...).

J’ai passé ensuite à l'apprentissage sur puce des réseaux de neurones impulsionnels. J’ai

décrit les différents éléments de l'apprentissage, la règle delta généralisée ainsi que son

adaptation au mode impulsionnel pour son implémentation sur puce. J’ai terminé cette partie

par présenter deux exemples qui illustrent la faisabilité et l'efficacité de cette architecture. Le

fruit de ces travaux est une communication dans la 13ème conférence internationale IEEE

Electronics, Circuits & Systems (ICECS Nice, France) intitulé : "FPGA Implementation of

Programmable Pulse Mode Neural Network with on Chip Learning for Signature

Application".

L’architecture du réseau de neurone étudié précédemment, basées sur le mode

impulsionnel, emploi le synthétiseur numérique de fréquence (DDFS) comme multiplicateur

de synapse. Ainsi la fonction non-linéaire d'activation peut être facilement réalisée par

saturation statistique.

Une des limitations de cette architecture est que les poids synaptique sont bornés et sont

compris entre -1 et +1, ce qui rend l’apprentissage difficile, particulièrement pour les réseaux

de neurones multicouches de grandes tailles. Une autre limitation pour ce type d’architecture

est que la précision de calcul du mode impulsionnel est inférieure à celle des neurones

arithmétiques entièrement numériques. En outre, la fonction d'activation du neurone

impulsionnel est affectée par le nombre de signaux d'entrée et par la distribution des poids

synaptiques, ce qui empêche l'apprentissage de converger rapidement.

Afin d’apporter des solutions à ces limitations, on a proposé une nouvelle architecture.

L’unité synaptique a été construite par des portes logiques AND et un bloc de concaténation.

L’unité neuronale caractérisée par une fonction d’activation programmable est obtenue par

une sommation pondérée de trois fonctions rampes. L’architecture du réseau de neurone

impulsionnel avec apprentissage sur puce est testée par simulation et implémentée sur FPGA

pour une validation. Les résultats de cette partie sont publiés dans une session spéciale sur les

réseaux de neurones impulsionnels de la 4ème conférence internationale IEEE Systems,

Signals and Devices (SSD, 19-22 Mars 2007, Hammamet, Tunisie). Le papier est intitulé :

"Implementation of a Pulse Stream-Based Neural Network with a Programmable Linear

Activation Function". Ces travaux sont aussi publiés dans la revu Transaction on Systems,

Signals ans Devices sous le titre "Implementation of a Pulse Stream-Based Neural Network

with a Programmable Linear Activation Function".

L’optimisation de l’architecture du réseau de neurones impulsionnels est une tâche très

importante pour accélérer au maximum le transfert des données et le processus

d’apprentissage sur puce. De ce fait, j’ai essayé d’optimiser les unités synaptiques et de

neurone. Par ailleurs, le synapse a été conçu en utilisant un additionneur et un registre pour

accomplir la multiplication des impulsions d’entrée par les poids synaptiques. L’architecture

du neurone construit à l’aide de trois fonctions rampes est réduite à une seule rampe avec un

circuit de raffinement des extrémités pour la rendre différentiable et semblable à la fonction

sigmoïde. La faisabilité de cette architecture a été testée, en proposant un système de

détection de contour, basé sur un réseau de neurones impulsionnels agissant en tant

qu’opérateur de Canny. Dans l'étape d'apprentissage, j’ai employé une base de données

d'images hétérogènes de trois classes, de 30 échantillons chacune. Des faibles erreurs

d'apprentissage et bons taux de généralisation sont obtenus. Le réseau de neurones

impulsionnels est implémenté sur une plateforme FPGA.

Travaux en cours :

Arrivé à ce stade, on veut entamer les étapes suivantes :

Conception d’un neurone à fonction d’activation radiale.

Validation de l’architecture du réseau de neurones impulsionnels à fonction

d’activation radiale avec une application de reconnaissance de formes de grande

résolution.

1

/

2

100%