Évolution des logiciels défensifs en vue d`une

C

CO

OM

MI

IT

TÉ

É

N

NA

AT

TI

IO

ON

NA

AL

L

F

FR

RA

AN

NÇ

ÇA

AI

IS

S

D

DE

E

R

RA

AD

DI

IO

OÉ

ÉL

LE

EC

CT

TR

RI

IC

CI

IT

TÉ

É

S

SC

CI

IE

EN

NT

TI

IF

FI

IQ

QU

UE

E

1

EVOLUTION DES LOGICIELS DEFENSIFS EN VUE D'UNE

AMELIORATION DE L'IMMUNITE DES SYSTEMES EMBARQUES

Rachid ALAOUI * - Etienne SICARD ** - Lahoussine BOUHOUCH *** -

Stéphane BAFFREAU **** - A MOUDDEN*****

(*) ETAR Sous Massa Draa, Agadir Maroc, [email protected]

(**) Université de Toulouse, INSA DGEI, 135 Avenue de Rangueil, 31077 Toulouse Cedex France

(***) Département Génie Electrique, EST Agadir, Université Ibn Zohr, B.P. 33/S, 80000 Agadir, Maroc

(****) Université de Toulouse, GEII IUT de Tarbes, 1 Rue Lautréamont, 65000 Tarbes, France

(*****) Laboratoire MCCM. Faculté des Sciences, Université Ibn Zohr, Agadir

Résumé. Pour améliorer l'immunité électromagné-

tique des systèmes embarqués, bien souvent les

concepteurs centrent leurs efforts sur la partie

matérielle. Cependant, de tels systèmes sont généra-

lement construits autour d'un ou plusieurs calcu-

lateurs. De ce fait, une approche complémentaire peut

être envisagée afin de diminuer la susceptibilité du

système final: le développement d'un logiciel défensif.

Dans cet article, nous présentons quelques méthodes

logicielles destinées à améliorer l'intégrité du système

tout en préservant sa fonctionnalité première.

I. INTRODUCTION

Les systèmes électroniques embarqués sont devenus

incontournables dans la vie actuelle de l'homme. Ils

sont partout présents, que ce soit dans les domaines du

transport, de la télécommunication, du médical, …

Les fonctions qu'ils doivent accomplir sont toujours

plus nombreuses, complexes, voire, dans bien des cas,

critiques pour l'intégrité des personnes qui les

utilisent. De plus, de part leur grande transportabilité,

ces systèmes peuvent évoluer dans des environ-

nements électromagnétiques très difficiles. La figure 1

illustre ce propos au travers de l'automobile qui peut

être soumise à de multiples sources d'agressions

électromagnétiques, de formes d'onde, d'amplitude et

de fréquences très différentes.

Composants

Moteurs électriqueTéléphone

Radar

Fig.1 – illustration de quelques sources d'agression

électromagnétique dans le domaine automobile.

Par ailleurs, ces systèmes présentent des similitudes

technologiques: leur architecture repose sur un ou

plusieurs circuits intégrés programmables.

Ces composants, pour une grande partie des micro-

contrôleurs, gèrent la fonctionnalité globale du

système. Aussi, leur immunité électromagnétique se

doit d'être la meilleure possible. Pour cela, deux types

d'approches complémentaires peuvent être effectuées.

La première se situe au niveau matériel. L'étude est

effectuée sur le composant lui-même, et peut être

complétée par une évaluation au niveau système [1],

[2], [3].

La seconde approche correspond à un traitement

logiciel spécifique. L'application informatique

développée doit non seulement effectuée les tâches

requises pour le système, mais elle doit également

prendre en compte et gérer au mieux les éventuelles

perturbations électromagnétiques extérieures [4], [5],

[6]. Dans la suite de cet article, nous nous

intéresserons uniquement à cette approche.

II. PROTECTIONS MATERIELLES

La détection et la correction matérielle d’une erreur

s’appuient toujours sur une architecture spéciale

souvent au niveau équipement, les composants restant

des éléments standard dans la plupart des cas

(Commercial-Off The Shelf).

Ces architectures existent au niveau circuit et sont

principalement destinées à parer les SEU (Single

Event Upset), dus à la pénétration d’une particule

(neutron, particule bêta, etc.) dans le composant. Ce

sont des effets localisés soumis à des lois probabilistes

(par exemple : la probabilité d’agresser les n circuits

redondants est très faible). Il existe des circuits de

type FPGA incluant des systèmes de corrections

automatiques mais ils représentent un surcoût

important pour l’équipement et sont peu utilisés.

L’agression par rayonnement électromagnétique

n’évoque pas les mêmes contraintes : le circuit peut

être agressé dans son ensemble et pas nécessairement

sur des I/O ou les alimentations. Dans un tel cas de

figure, tous les circuits redondants et de contrôle

2

peuvent être perturbés, d’où l’utilisation de l’approche

logicielle [7].

III. PRINCIPE DES LOGICIELS DEFENSIFS

Le développement d’un système sûr de fonction-

nement passe par l’utilisation combiné d’un ensemble

de techniques logicielles qui peuvent se résumer

comme suit :

• Prévention des fautes : comment empêcher

l’occurrence ou l’introduction de fautes ;

• Tolérance aux fautes : comment fournir un service à

même de remplir la fonction du système en dépit

des fautes ;

• Prévision des fautes : comment estimer la présence,

la création et les conséquences des fautes [8].

L'utilisation de ces techniques logicielles dans le but

d'améliorer l'immunité du système peut se faire à trois

niveaux différents.

Le premier se situe directement à l'interface entre le

micro-contrôleur et son proche environnement. Ceci

implique l'utilisation de techniques spécifiques de

traitement et d'analyse des signaux d'entrée/sortie [5].

Le second niveau correspond à la gestion des

informations internes au micro-contrôleur. A savoir,

principalement les données nécessaires pour la bonne

exécution de l'application logicielle. Dans ce cas,

l'étude porte sur l'intégrité des mémoires et met en

œuvre des techniques de duplication des données [9]

ou de code de redondance cyclique [10].

Enfin, le dernier niveau concerne l'exécution de

l'application elle-même. Ceci implique de mettre en

place des techniques et des indicateurs afin de

s'assurer que le flot de contrôle est bien respecté. Ce

sont ces dernières techniques que nous considérerons

dans la suite de l'article.

IV. DESCRIPTION DES METHODES DE

GESTION DU FLOT DE CONTROLE

Afin de gérer au mieux le flot de contrôle d’une

application, il existe de nombreuses techniques de

protection logicielle. Dans les paragraphes suivants,

nous nous focaliserons sur trois d’entre elle : la

duplication du code par expressions régulières, la

gestion par signatures ainsi que la gestion par

identifiants.

IV.1 DUPLICATION DU CODE PAR

EXPRESSIONS REGULIERES

Cette technique consiste à dupliquer le code d'un

programme initial en créant un programme copie [6].

Ce second programme exécute des instructions

similaires à celui d'origine en manipulant des données

modifiées. La figure 2 présente un exemple de

transformation: une multiplication par un facteur -2.

Au final, on exécutera les deux programmes puis l'on

comparera les résultats obtenus pour savoir si

l'exécution s'est correctement déroulée.

Code initial Code dupliqué

x = 1 ;

y = 5 ;

i = 0 ;

tant que (i < 5)

{

z = x + i* y ;

I = i + 1 ;

}

i = 2 * z ;

x = - 2 ;

y = -10 ;

i = 0 ;

tant que (i > -10)

{

z = x + i * y / (-2) ;

i = i + (-2);

}

i = (-4) * z / (-2) ;

Fig. 2: Principe de la duplication du code par

expressions régulières

IV.2 GESTION PAR SIGNATURES

Dans cette technique, nous partons du principe qu'un

programme est un conglomérat de blocs ou nœuds

(Ni) de codes (procédures et fonctions) [11]. Un nœud

ne peut contenir d’instructions de branchement ou de

saut en dehors de la première et de la dernière

instruction. Une signature notée Si et une différence

de signature notée di sont assignés à chaque nœud

(Fig. 3).

N1

N2

G1=S1

G2=S2

S1

d1

S1

D2=S1 ⊕ S2

Branchement correct

N1

N2

G1=S1 S1

d1

Branchement incorrect

N3

N4

G4 ≠S4

S3

D3

Branchement illégal

Gn : signature courante du noeud Nn

Sn : Signature assignée au noeud Nn

dn : Difference de signature

Fig.3: Principe de la gestion par signatures.

Un registre de signature générale (G) est réservé pour

stocker la signature du nœud en cour d’exécution.

Pendant l’exécution normal du nœud Ni, la valeur de

G = Gi = Si. Si ce registre a une valeur différente de la

valeur assignée au nœud courant, cela signifie qu’il y

a une erreur dans le programme.

Lors d'un changement de nœud, une nouvelle

signature est générée par une fonction. Cette mise à

jour est effectuée en considérant les deux valeurs

associée à chaque bloc Ss (source) et Sd (destination).

Ces deux signatures déterminent le prochain

branchement.

IV.3 GESTION PAR IDENTIFIANTS

Le principe (Fig. 4) est similaire à la gestion par

signatures. Cependant, la fonction XOR est remplacée

par la fonction concaténation. Un identifiant (IDB) est

assigné à chaque nœud et un code à chaque

branchement. Un registre est réservé pour recevoir

l’identifiant de départ et d’arrivé. Une fonction F

calcule la nouvelle valeur et la compare avec le

nouveau bloc éventuel de branchement. Le

branchement s’établi et le registre se met à jour s’il

n’y a pas eu d’erreur sinon une procédure de gestion

d’erreur est déclenchée.

3

N2

N1

IDB2=0x20

IDB1=0x30

R=br12

F=0x20

F2=F1| IBC2

Si F? R erreur

br12=0x2030

Fig.4: Principe de la gestion par identifiants.

V. EXPERIMENTATION

Nous proposons de tester les concepts évoqués sur une

plate-forme conçu autour d’un micro-contrôleur

S12X. Le composant Freescale MC9S12XDP512 est

un micro-contrôleur 16 bits développé en 2005,

principalement destiné aux applications automobiles.

Ce composant de faible coût de revient, ayant une

faible consommation, intègre deux cœurs de calcul: un

processeur 16 bits de technologie CISC et un co-

processeur, la XGate, de technologie RISC. Ce dernier

a pour principal objectif la gestion des événements

d’interruption. Ce qui permet au processeur de se

focaliser sur l’exécution d’une tâche de fond. Le lien

entre les deux unités s’effectue alors au travers des

zones de mémoire données. La figure 5 présente un

diagramme de bloc simplifié de ce circuit intégré.

RAM 32 ko Flash 512 ko EEPROM 4 ko

Co-Processeur XGATE

Processeur S12X

Interruption

Temps Réel

119

Entrées/Sorties

PWM

sur 16 bits

5 Contrôleur

de Bus CAN

Convertisseur

A/D 10 bits

SPI, SCI, I²C,

Fig.5 – Diagramme de bloc simplifié du micro-

contrôleur S12X.

Afin d’évaluer l’impact du logiciel défensif sur la

susceptibilité du micro-contrôleur aux agressions de

type interférences 1MHz-3GHz, une carte de test a été

développée. Cette carte est réalisée sur un substrat de

type FR4, au format TEM/GTEM (10,3 x 10,3 cm).

Un premier plan de masse sur lequel est isolé le

micro-contrôleur permet de clore électriquement la

cage de Faraday constituée par la cellule TEM (Fig. 6

à gauche). Le second plan est constitué d’un plan de

masse et de quelques signaux. La troisième couche est

principalement un plan d’alimentation. La dernière

couche correspond à un plan de masse et de signaux.

C’est sur cette dernière couche que les composants et

connecteurs nécessaires au bon fonctionnement du

composant sont montés (Fig. 6 à droite).

Fig.6 – Caractéristiques de la carte de test.

La carte de test est étudiée pour faciliter l’injection de

perturbations radiofréquences par couplage capacitif

selon la méthode « Direct Power Injection » (DPI)

décrite dans la norme IEC 62132-2 [12]. Pour limiter

les réflexions du signal d’agression, les pistes

d’injection sont adaptées 50 Ω par un choix judicieux

de largeur de piste de circuit imprimé. Les

connecteurs câble/circuit sont de type SMB, égale-

ment adaptés 50 Ω. Les capacités de couplage et les

connecteurs sont situés au plus proche du point

d’entrée dans le composant de façon à minimiser la

longueur des pistes non adaptées. Parmi les

différentes points fonctionnels pouvant être agressés

on note le réseau d’alimentation, l’horloge et des

entrées/sorties analogiques et numériques.

De par les caractéristiques de la carte de test, d’autres

méthodes d’agressions sont envisageables: agression

par boucle magnétique en champ proche selon la

nouvelle proposition IEC 62132-9, ou encore

agression globale en cellule TEM/GTEM ou TEM

miniature telle que présentée par [13].

Une description du banc de mesure est donnée à la

Figure 7. Le banc de test utilisé repose sur le principe

de mesure DPI. La perturbation est créée par un

générateur de signaux radio-fréquence, puis amplifiée

avant d’être injectée dans le composant sous test au

moyen d’une capacité de couplage. Un oscilloscope

particulier analyse en temps réel les signaux émis par

le micro-contrôleur et déclenche une interruption

lorsque le signal « utile » sort du gabarit prédéfini. Le

signal utile correspond à un signal carré généré par

l’application logicielle embarquée. Les appareils de

contrôle et de mesures sont connectés entre eux par un

bus IEEE et gérés par un logiciel spécifique

développé au laboratoire.

Fig.7 – Banc de mesure utilisé pour les

expérimentations.

4

Le critère de susceptibilité retenu pour la mesure

correspond à une fluctuation du signal de sortie du

micro-contrôleur supérieure à 20% de sa valeur

nominale en tension et en décalage temporel. Pour une

fréquence de perturbation donnée on détermine le

moment où le signal sort du gabarit. Cette tâche est

grandement simplifiée par l'oscilloscope intégrant un

système temps réel de détection de sortie d’enveloppe.

La puissance est mesurée à l’aide d’un coupleur.

VI. EVALUATION

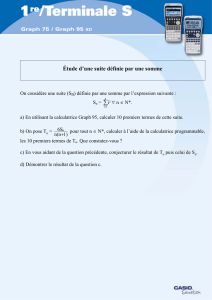

Afin d’évaluer l’impact au niveau logiciel, nous avons

utilisé un programme de référence, nommé par la suite

code conventionnel, et nous l’avons comparé aux trois

techniques de protection logicielle. Cette évaluation

considère l’espace mémoire utilisé ainsi que le temps

d’exécution nécessaire. Le tableau 1 synthétise les

résultats mesurés en terme d’occupation mémoire et

de temps d’exécution des différents codes.

Techniques CC

OC-TE

CT

OC-TE

Augmentation

relative en %

Expressions

régulières

96octets

48µs

219 octets

109 µs 127

Signatures 18 octets

9 µs

37 octets

18.5 µs 105

Identifiants 27 octets

13.5 µs

52 octets

26 µs 93

Tableau1 : Occupation mémoire et temps d’exécution.

CC : Code conventionnel.

CT : Code avec technique de protection logicielle.

OC : Occupation mémoire.

TE : Temps d’exécution.

Quelque soit le logiciel défensif considéré, l'espace

mémoire nécessaire et le temps d’exécution sont plus

que doublés. Par ailleurs, il est important de remarqué

que la taille du code conventionnel est très limitée. De

ce fait, l’ajout de quelques lignes de code

supplémentaire a un impact très fort sur ces deux

paramètres. De plus, les programmes ont été réalisés

sans la prise en compte des nouvelles stratégies de

programmation offerte par les circuits intégrés multi-

cœurs. Par conséquent, une optimisation reste encore

possible pour chacun des logiciels.

CONCLUSION

Dans cet article, nous avons décrit la problématique

de la susceptibilité électromagnétique des systèmes

embarqués. De plus, des techniques de protection

logicielle pour améliorer la bonne exécution du flot de

contrôle ont été présentée, ainsi qu'une mise en œuvre

expérimentale. Enfin, les coûts en temps et espace

mémoire nécessaire pour la mise en œuvre de ces

techniques ont été évalués.

REFERENCES

[1] A. Boyer, S. Akue Boulingui, S. Bendhia, E.

Sicard, S. Baffreau, "A methodology for

predicting by near field chip to chip coupling"

EMC Compo 07, Torino Italy, November 2007 .

[2] A. Z. H. Wang, "On-chip ESD protection for

Integrated circuits", An IC Design Perspective,

Kluwer Academic Publishers, 2002, ISBN

0-7923-7647-1

[3] IEC 62014-3: 93/146/CDV, "EMC for

Component, Integrated Circuits Electrical

Model (ICEM)", Document online at

http://www.ic-emc.org

[4] S. Baffreau, L. Tysk, G. Motet, "Détection

logicielle des défaillances d'une plate-forme

matérielle dues à des champs électromagné-

tiques", CEM'04, Toulouse France, Mars 2004.

[5] D. Campbell, "Defensive software programming

with embedded microcontrollers", IEE

Colloquium on Electromagnetic Compatibility

of Software, Birmingham, UK, 1998.

[6] M. Rebaudengo, M. S. Reorda, M. Torchiano,

M. Violante, "Soft-error detection through

software fault-tolerance techniques", IEEE

International Symposium Defect Fault

Tolerance in VLSI Systems, Austin, USA,

November 1999, pp. 210-218.

[7] Enrique LAMOUREUX, " Etude de la

susceptibilité des Circuits intégrés numériques

aux Agressions hyper-fréquences", Chap.2,

Thèse No 817, INSA-TOULOUSE, 25 janvier

2006.

[8] J.C. Laprie, " Guide de la sûreté de

fonctionnement", Cépaduès-Editions, Paris

1995,pp 7-8,

[9] N. Oh, S. Mitra, E. J. McCluskey, "ED4I: Error

Detection by Diverse Data and Duplicated

Instructions", IEEE Transaction on Computers,

Vol. 51, N°2, pp. 180-199, February 2002.

[10] ISO 11898 Controller Area Network (CAN) for

high speed communication.

[11] N. Oh, P. P. Shirvani, E. J. McCluskey,

"Control-flow checking by software signatures",

IEEE Transaction on Reliability, Vol. 51,

pp. 111-122, March 2002.

[12] IEC 62132 part 2, 47A/529/NP, "Direct RF

power injection to measurement method".

[13] B. Körber, M. Trebeck, N. Müller, F. Klotz,

"IC-Stripline – A new proposal for susceptibility

and emission testing of ICs", 6

th International

work shop on electromagnetic compatibility of

integrated circuit EMC Compo, Torino (Italy),

November 2007.

1

/

4

100%

![III - 1 - Structure de [2-NH2-5-Cl-C5H3NH]H2PO4](http://s1.studylibfr.com/store/data/001350928_1-6336ead36171de9b56ffcacd7d3acd1d-300x300.png)