énoncé

•,1,2 1 2

•,1,2 1 −2

•,[ + ] +

•1,[ + ] 1+

•1,2,1=2+ 1

•,

•1,2 1 1

•

•

•

•

•

•

•

•

•

•

•

•

8×210

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

∗

∗

∗

∗

∗

∗

∗

∗

∗

∗

∗

∗

•

•

∗

∗

∗

∗

•

•

•

•

•

•

•

6

6

7

7

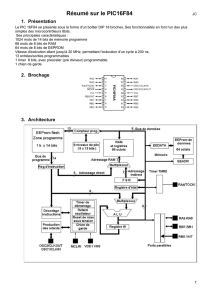

1

/

7

100%