XIV – Oscillateur à portes logiques I - Les portes logiques

TP : A – Electronique XIV – Oscillateur à portes logiques Sciences Physiques : PSI

Laurent Pietri ~ 1 ~ Lycée Henri Loritz - Nancy

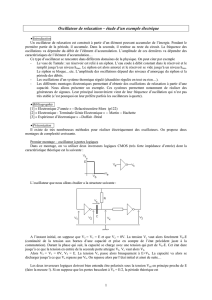

I-1) Document 1 : Principe d’une porte logique

En électronique, une porte logique est un composant fonctionnant en régime saturé, et dont

l'unique sortie ne peut prendre que deux valeurs de tensions (par exemple 0V ou 15V), notées 0 (pour

0V par exemple) ou 1 (pour 15V par exemple).

La valeur de cette sortie dépend :

- De la valeur de l'entrée (0 ou 1) pour les portes logiques à une entrée

- Des valeurs des entrées (0/0 ou 0/1 ou 1/0 ou 1/1) pour les portes logiques à deux entrées.

I-2) Document 2 : Table de vérité

Sur le tableau suivant on peut voir les différents types de porte et leur table de vérité :

Ces portes suivent donc une logique booléenne et peuvent donc permettre de faire du traitement du

signal numérique.

XIV – Oscillateur à portes logiques

Objectifs :

Après avoir vu le composant CMOS 4011 qui nous permettra de réaliser des fonctions (ou portes)

logiques, on utilisera celui-ci pour réaliser un oscillateur.

I - Les portes logiques

TP : A – Electronique XIV – Oscillateur à portes logiques Sciences Physiques : PSI

Laurent Pietri ~ 2 ~ Lycée Henri Loritz - Nancy

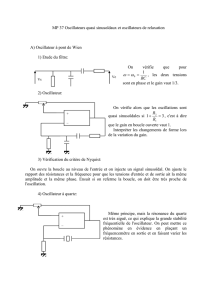

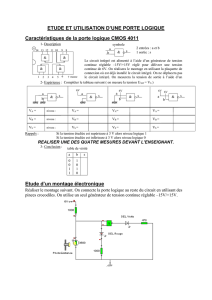

I-3) Document 3 : Le compostant CMOS 4011 et porte NAND

Nous allons utiliser le composant CMOS 4011, pour réaliser des portes logiques :

Ce composant sera alimenté par une tension continue de VDD = 15V (il peut l’être aussi en 5 ou

10V – Borne 14) par rapport à la masse (Ground – Borne 7). La valeur 1 d'une porte NAND donnée

correspond à un potentiel de sortie de 15V et la valeur 0 au potentiel nul. On remarque que ce

composant est constitué de 4 portes NAND de technologie CMOS.

A partir du tableau précédent, la table de vérité d'une porte NAND peut se résumer par :

La sortie a la valeur 1 si les entrées n'ont pas simultanément la valeur 1.

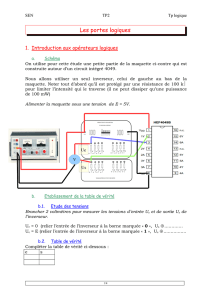

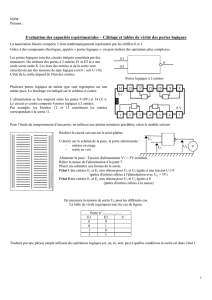

I-4) Document 4 : Plaque Labdec

Nous allons utiliser une plaque Labdec pour réaliser nos différents montages :

Ce type de plaque est très utilisé en électronique. Elle est constituée de lignes A,B,C,D,E et de colonnes

numérotées de 1 à 43.

- La ligne A est reliée à la borne A bleue, la ligne B à la borne rouge et la ligne E à la borne noire

(masse). Les bornes de ses lignes sont reliées entre eux comme pour C et D.

- Les colonnes sont décomposées en deux parties, par exemple la colonne 10 a ses

contacts (klmno) reliés entre eux et de même pour la partie (fghij).

Pour mieux comprendre les connexions on pourra se fier au schéma suivant qui montre les connexions

des bornes de la plaque labdec :

TP : A – Electronique XIV – Oscillateur à portes logiques Sciences Physiques : PSI

Laurent Pietri ~ 3 ~ Lycée Henri Loritz - Nancy

I-5) Autre porte logique : NO

En pratique, on peut réaliser tout type de porte en combinant des portes NAND, par exemple, on

peut facilement réaliser une porte NO. Pour cela, on relie électriquement les deux entrées d'une porte

NAND :

Construire la table de vérité de cette porte logique, et en déduire sa fonction NO.

e

s

0

1

II - Étude expérimentale de portes logiques

Dans toute la suite, on alimente le CMOS 4011 par une tension continue de 15V.

II-1) Porte NO

- Réaliser une porte NO à l'aide du CMOS 4011. (Vérifier bien les branchements de l’alimentation

+15V/0V et celle de l’alimentation variable)

En faisant varier la tension d'entrée E de 0 à 15V, vérifier la table de vérité d’une porte NO et

déterminer le seuil de basculement Vb entre l’état logique 0 et l’état logique 1 lorsque E augmente, puis

lorsque E diminue.

- Représenter alors le potentiel de sortie en fonction du potentiel d'entrée. On fera apparaître :

o La tension de basculement Vb.

o Les tensions correspondant à l’état 0 et à l’état 1 (noté VDD par la suite)

II-2) Porte NAND

- Vérifier électroniquement la table de vérité d’une porte NAND en adoptant comme tension

d’entrée 15V pour le niveau logique 1 et 0V pour le niveau logique 0.

III - Oscillateurs à porte logiques

III-1) Oscillateur à une porte

- Réaliser le circuit suivant :

- Justifier que ce montage est un oscillateur.

- Mesure la période d’oscillation de l’oscillateur

- Comparer cette valeur au temps de commutation de la porte fournie dans le datasheet. Conclure.

TP : A – Electronique XIV – Oscillateur à portes logiques Sciences Physiques : PSI

Laurent Pietri ~ 4 ~ Lycée Henri Loritz - Nancy

a) Document 5 : Analyse théorique

On va réaliser le circuit suivant avec R=105Ω, R'=106Ω, C=10nF à 100nF

On va démontrer que la période de cet oscillateur peut se mettre sous la forme :

On justifie cette période par le raisonnement suivant, en négligeant les temps de commutation. Pour

simplifier l’analyse, on néglige la résistance de sortie des portes logiques et on considère leur résistance

d’entrée comme infinie. La résistance R’ ne joue donc aucun rôle dans l’étude théorique de l’oscillateur

(elle protège la porte logique). Ainsi à tout instant :

- Supposons une phase pour laquelle on ait :

On a donc et le condensateur est en cours de charge. Cette phase s’achève lorsque

VE2=Vb. Si l’on choisit cet instant comme origine des temps, on a donc :

o

o

Or :

car on néglige le courant dans R’.

Or jusqu’au prochain basculement on a : donc :

On a basculement quand

- Lors de la phase suivante on a :

o

o

On a donc :

qui s'écrit cette fois :

Or à

Donc :

On a basculement quand :

On remarque que : , le signal serait, avec nos approximations, symétrique.

III-2) Oscillateur à deux portes

TP : A – Electronique XIV – Oscillateur à portes logiques Sciences Physiques : PSI

Laurent Pietri ~ 5 ~ Lycée Henri Loritz - Nancy

III-3) Document 6 : Datasheet CMOS 4011

b) Partie expérimentale

- Réaliser le montage sur la plaquette labdec

- Visualiser les signaux vs1 et ve2. Représenter les deux signaux sur votre compte-rendu.

- Vérifier la période du signal.

- Donnez votre résultat de T. Conclure.

1

/

5

100%