Slide Template - Lab

Contribution au domaine de la conception des

Systèmes Embarqués Reconfigurables

Guy GOGNIAT

Université de Bretagne Sud

Laboratoire LESTER

CNRS FRE 2734

Habilitation à Diriger des Recherches

Lorient, Vendredi 26 octobre 2007

Source: Xcell Journal Issue 58

2

Agenda

•Quelques faits marquants…

•Domaines de recherche et contributions

Systèmes embarqués (HW/SW codesign)

Architectures reconfigurables

Sécurité des systèmes embarqués

•Et demain…

•Enseignement et recherche…

3

Quelques faits marquants…

1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010

IP Based

design NoCMPSoC RTOS

Cryptoprocesseur MPSoC Adaptatif

Architecture

Profil MARTESystemC UML TLM

Langage

Cœur de processeur

Blocs DSP

Mémoire

Architectures

reconfigurables

Gros grain

Reconfiguration

dynamique

Saut en

complexité des

FPGA

Reconfigurable

Radio Logicielle

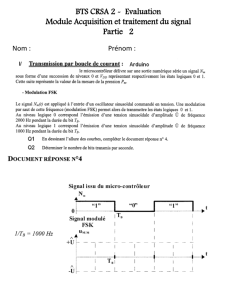

AES ECC

2,5G (100kbit/s) 3G (2Mbit/s) 4G (1Gbit/s)

MPEG2 MPEG4 H264

Application

EASI Tools Suite

(Beach Solutions)

PICO Express

(Synfora)

Platform Architect

(CoWare) Catapult C

(Mentor Graphics)

Outils

industriels

4

Quelques faits marquants…

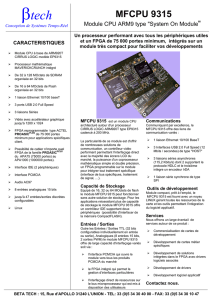

Circuit MP211 pour les applications

téléphone cellulaire/NEC

2005

1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010

Architectures

reconfigurables

Gros grain

Saut en

complexité des

FPGA

MPSoC

Cryptoprocesseur

Circuit multistandard WLAN

(802.11a et MCCDMA)/ST

Microelectronics

2003

Intégration grain fin/gros grain

Hiérarchie de bus

Conception à base d’IP

Multiprocesseur

Processeurs dédiées

Cryptographie

2D/3D

Traitement image/signal

5

Quelques faits marquants…

Circuit Tera-scale/Intel

2007

SoC pour la HDTV

Laurent Ducousso/STMicroelectronics

Colloque national 2007/GDR SoC-SiP

60-62 millions de lignes de code embarqué

4-5 millions de lignes de code RTL (700 bibliothèques RTL)

16 processeurs embarqués

115 domaines d’horloge

Chiffrement de toutes les communications avec les mémoires externes

Architecture de communication-5Goctet/s

1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010

MPSoC Adaptatif

Saut majeur en

complexité

Limite des solutions

à base de bus

Intégration massive

Migration vers le tout processeur

Processeurs dédiés

Réseau de communication

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

1

/

50

100%