LE BUS PCI 10 ième partie: Le futur du Bus PCI

1

LE BUS PCI

10ième partie: Le futur du Bus PCI

Sommaire - Repère

Dixième partie Le futur du Bus PCI

1ière partie: Présentation

2ième partie: Les signaux

3ième partie: Les échanges de données

4ième partie: L’Arbitrage

5ième partie: Les transactions particulières

6ième partie: Les aspects électriques, timings

7ième partie: Bridge PCI / PCI

8ième partie L’espacedeconfiguration

9ième partie Les performances

Cours_bus_PCI_8_02

2

LE BUS PCI

10ième partie: Le futur du Bus PCI

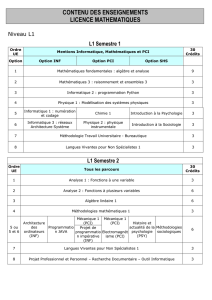

Les standards possibles

Tendances: Bus étroits / séries, point-à-point, bande passante élevée

Facilitel’augmentationdesfréquences

Moins de problème de skew

Faciliteladiminutiondestensionsd’alimentation

Facilite la conception des cartes

3

LE BUS PCI

10ième partie: Le futur du Bus PCI

Les standards possibles

PCI 32 bits 33 MHz 84 broches 133 Mo/s

PCI-X 64 bits 133 MHz 150 broches 1 Go/s

Rapid I/O 1 bits 2,5 GHz 4 broches 312 Mo/s/dir

Série 2,5 GHz 4 bits 2,5 GHz 10 broches 1,25 Go/s/dir

HyperTransport 4 bits 800 MHz 24 broches 1,6 Go/s/dir

8 bits 800 MHz 40 broches 3,2 Go/s/dir

16 bits 800 MHz 76 broches 6,4 Go/s/dir

32 bits 800 MHz 148 broches 12,8 Go/s/dir

3GIO 8 bits / dir 40 broches 2,5 Go/s

PCI Express

4

LE BUS PCI

10ième partie: Le futur du Bus PCI

Le bus Rapid I/O

Motorola

•Bus point-à-point

•Permet l ’interconnexionde

•CPU

•Mémoire

•I/O

•Full duplex

•Réseau commuté (déterministe)

•Niveau LVDS (2,5V)

•Incompatible avec la version

parallèle

CPU CPU

Mémoire Mémoire

Commutateur

Rapid I/O

CPU ASIC

FPGA

Commutateur

Rapid I/O

Mémoire

DSP DSP DSP DSP

Commutateur

Rapid I/O Rapid I/O

vers PCI

PCI

Commutateur

Rapid I/O

Sous-système DSP Sous-système PCI

Sous-système Hôte Sous-système de contrôle

Rapid I/O

5

LE BUS PCI

10ième partie: Le futur du Bus PCI

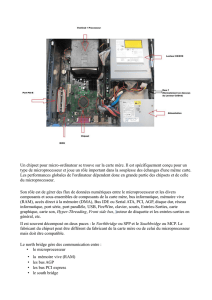

Le bus HyperTransport

AMD

CPU

CPU

Contrôleur

Mémoire

DRAM

DRAM

AGP

Pont

PCI_X Circuit

E/S Pont

PCI South

Bridge

Bus HyperTransport chaîné

PCI_X PCI

PCI

•Protocole compatible PCI et PCI-X

•Niveau électriques LVDS (1,2V)

•Chaque E/S du bus inclut 2 liaisons point-à-point

unidirectionnelles

•Chaque liaison inclut:

•1 chemin de données de 1, 4, 8, 16 ou 32 bits

•les signaux d ’horlogeetdecommande

•Le bus peut être asymétrique

Contrôleur

Mémoire

DRAM

DRAM

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%