mon diaporama

CONCEPTION D'UN OS

-ETAPE 2 -

Segmentation

et

Interruptions

IR3 par Brice Fournier

Configurer le processeur pour qu'il interagisse

proprement avec la mémoire et les périphériques.

Segmentation

–Principes

–Fonctionnement

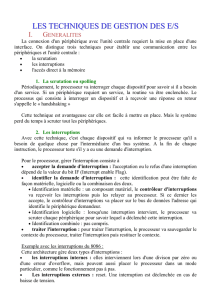

Interruptions

–Principes

–Types

–Les Contrôleurs

–IDT

–Fonctionnement

d'une routine

Pratique

Exemple

PLAN

BUT :

Adresser la totalité de l'espace mémoire

physique possible

0-4 Go sans souci.

➢Isolation des programmes les uns des autres.

➢Définition de niveaux de privilèges pour certaines opérations.

Principes :

SEGMENTATION 1/5

Différents types d'adresses :

➢Logiques

➢Linéaires

➢Physiques

SEGMENTATION 2/5

SEGMENTATION 3/5

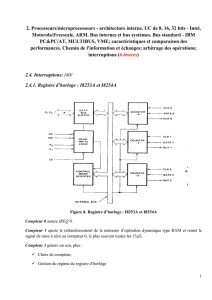

MMU : Unité de Gestion de la mémoire chargée de la

traduction des adresses

➔Le processeur ne voit que les adresses logiques

GDT : Global Descriptor Table

-> globale à tout le système (Obligatoire)

LDT : Local Descriptor Table

-> Propres à chaque tâche

Tables de traduction d'adresses :

La segmentation permet de définir des segments personnalisés en

terme de taille, de positionnement ou de droits d'accès.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%