Rappels de cours

Architecture des machines 2003/2004 Joëlle Delacroix

1

EXERCICES DIRIGES 10-11

BUS

ENTREES / SORTIES

INTERRUPTIONS

Rappels de cours

Le processeur dialogue avec les unités d'échanges via un circuit d'interface ou unité d'échange.

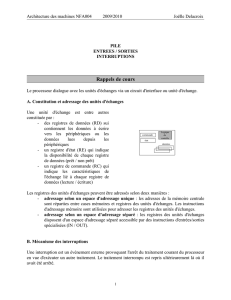

A. Constitution et adressage des unités d'échanges

Une unité d'échange est entre autres

constituée par :

- des registres de données (RD) sui

contiennent les données à écrire

vers les périphériques ou les

données lues depuis les

périphériques

- un registre d'état (RE) qui indique

la disponibilité de chaque registre

de données (prêt / non prêt)

- un registre de commande (RC) qui

indique les caractéristiques de

l'échange lié à chaque registre de

données (lecture / écriture)

commande

état

données

Logique

de

contrôle

Les registres des unités d'échanges peuvent être adressés selon deux manières :

- adressage selon un espace d'adressage unique : les adresses de la mémoire centrale

sont réparties entre cases mémoires et registres des unités d'échanges. Les instructions

d'adressage mémoire sont utilisées pour adresser les registres des unités d'échanges.

- adressage selon un espace d'adressage séparé : les registres des unités d'échanges

disposent d'un espace d'adressage séparé accessible par des instructions d'entrées/sorties

spécialisées (IN / OUT).

B. Mécanisme des interruptions

Une interruption est un événement externe provoquant l'arrêt du traitement courant du processeur

en vue d'exécuter un autre traitement. Le traitement interrompu est repris ultérieurement là où il

avait été arrêté.

Architecture des machines 2003/2004 Joëlle Delacroix

2

La prise en compte des interruptions peut être interdite : c'est le masquage des interruptions.

Deux instructions machine sont liées à cette opération :

- EI : Enable Interrupt : autorise la prise en compte des interruptions en positionnant le

bit I du registre PSW à 0

- DI : Desable Interrupt : n'autorise pas la prise en compte des interruptions en

positionnant le bit I du registre PSW à 1

La prise en compte d'une interruption s'effectue avant le commencement d'un nouveau cycle

d'instruction.

Le traitement d'une interruption comporte les phases suivantes :

1/ Acquittement de l'interruption , masquage des interruptions, sauvegarde de CO, PSW et

éventuellement des registres généraux, démasquage des interruptions

2/ Calcul de l'adresse de la routine d'interruption, branchement à cette adresse.e et

exécution de la routine d'interruption

3/ Retour de la routine d'interruption par le biais de l'instruction RTI qui restaure le

contexte sauvegardé à l'étape 1.

C. Gestion des transferts entre le processeur et les unités d'échanges

Il existe trois modes de gestion de ces transferts :

- entrées/sorties programmées : le processeur interroge en permanence l'unité d'échange

pour savoir si elle est prête ou non pour un nouveau transfert de donnée.*

- entrées/sorties par interruption : l'unité d'échange signale par une interruption qu'elle

est prête à accepter un nouveau transfert.

- entrées/sorties par DMA : l'unité DMA

(Direct Memory Access) permet à l'unité

d'échange d'accéder seule à la mémoire

centrale. Une opération d'entrées/sorties

s'effectue alors selon les étapes suivantes

:

- initialisation du Dma par le

processeur pour décrire l'opération

d'entrées/sorties à effectuer

- transfert des données par le Dma

- émission d'une interruption par le

Dma en fin d'opération

CPU

Mémoire centrale

nbO octets

AdM

nbO

AdM

@p

sens

@p

DMA

.

Exercices

Architecture des machines 2003/2004 Joëlle Delacroix

3

Exercice 1

Soit la séquence de code assembleur suivante où Rg désigne un mode d'adressage avec un seul

opérande registre:

SAUVE : DI

PUSH Rg CO

PUSH Rg PSW

PUSH Rg R0

PUSH Rg R1

PUSH Rg R2

PUSH Rg R3

PUSH Rg R4

PUSH Rg R5

EI

a/ Quel est le rôle des instructions EI et DI ?

b/ Dans quel but ces deux instructions sont-elles utilisées ici ?

c/ Quel(s) événement(s) survenant au niveau du processeur peut (peuvent) provoquer l'exécution

de ce code ?

Exercice 2

a/ Rappelez en quelques lignes le rôle des interruptions dans le mécanisme des entrées-sorties.

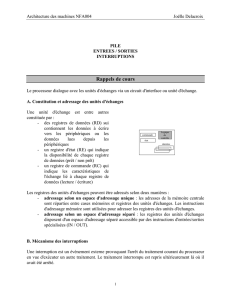

b/ On considère une machine admettant 8 niveaux d’interruptions matérielles numérotées de 0 à

7, le niveau d’interruptions 0 étant le plus prioritaire et le niveau 7 le moins prioritaire. Le

processeur dispose de deux broches, une broche INT sur laquelle lui parvient le signal

d’interruption, une broche INTA avec laquelle il acquitte les interruptions. Les 8 niveaux

d’interruptions sont gérés par un contrôleur d’interruptions de type circuit 8259A qui possède

deux registres de 8 bits chacun, lui permettant de gérer les requêtes d’interruptions et leurs

priorités. Le premier registre appelé registre ISR mémorise le niveau d’interruption en cours de

traitement en positionnant à 1 le bit correspondant à l’interruption en cours de traitement. Le

second registre IRR mémorise les interruptions reçues par le contrôleur en positionnant à 1 le bit

correspondant à l’interruption reçue, cette mémorisation durant jusqu’à ce que l’interruption ait

été traitée par le processeur.

Les priorités sur les interruptions fonctionnent de la manière suivante : lorsque le

processeur traite une interruption de niveau i (le bit i du registre ISR est alors à 1), toutes les

interruptions de priorité inférieure ou égale à i parvenant au contrôleur sont mémorisées dans le

registre IRR, mais elles ne sont pas délivrées au processeur. Elles seront délivrées selon leur

ordre de priorité, ultérieurement, dès que le traitement de l’interruption i aura été achevé. Une

interruption de priorité supérieure au niveau i est au contraire délivrée au processeur et

interrompt le traitement de l’interruption i en cours qui est repris ultérieurement, une fois le

traitement de l’interruption plus prioritaire achevé.

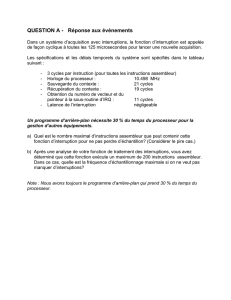

b1/ Considérez l’état courant du contrôleur et du processeur donné sur le figure ci-

dessous. Que se passe-t-il ? Que va faire le processeur ?

Architecture des machines 2003/2004 Joëlle Delacroix

4

b2/ En partant de l’état précédent, décrivez la suite des opérations tant au niveau du

contrôleur (évolution des registres ISR et IRR) que du processeur si l’on considère que

surviennent simultanément au contrôleur les interruptions 1 et 5.

Processeur

Mémoire Centrale

Contrôleur d’interruptions

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

IRR

ISR

0 0 0 0 0 1 0 0

0 0 0 0 0 1 0 0

1023

Co

INT

INTA

lec

ecr

bus de données

bus d’adresses

0

1

2

3

4

5

6

7

100

110

120

130

140

150

160

170

Table des vecteurs

d’interruptions

100

170

ROUTINES

D’INTERRUPTIONS

1023 Programme

utilisateur

It 2

Unité

d’échange

Unité

d’échange

Unité

d’échange

It 2

Exercice 3

On considère une machine disposant d'un espace d'adressage unique. Elle représente les nombres

signés en complément à 2.

Une unité périphérique de type imprimante est considérée. ETAIMP est le registre d'état de

l'imprimante tel que le bit de poids fort de ETAIMP est à 1 si l'imprimante est prête et à 0 sinon.

SORIMP est le registre de données de l'imprimante.

Question 1

L'instruction suivante permet de tester le signe du contenu d'un registre : TESTS Rg1 Reg.

TESTS positionne le bit S du registre d'état PSW.

Que réalise le programme ci-dessous ?

Initialisation des registres RIX et R1

LOAD Im RIX EMPL

LOAD Im R1 80

ATTENTE :

LOAD D R2 ETATIMP

TESTS Rg1 R2

JMPP Im ATTENTE

LOAD Ix R3, 0

STORE D R3, SORIMP

ADD Im RIX, 1

Architecture des machines 2003/2004 Joëlle Delacroix

5

ADD Im R1, -1

JMPZ Im FIN

JMP Im ATTENTE

FIN : STOP

Question 2

On suppose à présent que la fin de transfert de chaque caractère par l'unité d'échange vers

l'imprimante est signalée par une interruption. Commentez le code ci-dessous en expliquant son

rôle.

DI

ADD Im R1, -1

JMPZ Im FIN

LOAD Ix R3, 0

STORE D R3, SORIMP

ADD Im RIX, 1

FIN : RTI

Exercice 4 (cet exercice est tiré du livre Organisation et Conception des ordinateurs, D.

Patterson – J. Hennessy)

On considère trois périphériques : un souris, une unité de disquette et une unité de disque dur.

Question 1

Les trois périphériques sont gérés par entrées/sorties programmées. Une opération d'interrogation

d'un périphérique coûte 100 cycles horloge. L'horloge processeur fonctionne à une fréquence de

50 MHz.

- La souris doit être interrogée 30 fois par seconde pour être sûr de ne manquer aucun

mouvement de l'utilisateur.

- La disquette transfère des données au processeur par blocs de deux octets et possède un

débit de 50 Ko/seconde.

- Le disque transfère des données au processeur par blocs de quatre octets et possède un

débit de 2 Mo/seconde.

Calculez la fraction de temps processeur consommée pour la gestion de chacun des périphériques

Question 2

On considère à présent que l'unité de disque est gérée par DMA. L'initialisation du DMA par le

processeur nécessite 1000 cycles horloge. Le traitement de l'interruption en fin de transfert DMA

nécessite 500 cycles horloge. Chaque transfert DMA concerne 4 Ko de données et le disque est

actif à 100 %.

Quelle est la fraction de temps processeur consommée par la gestion de l'unité DMA ?

Exercice 5

6

6

1

/

6

100%