PDF-1

École de technologie supérieure Session : Hiver 2002

Département de génie électrique Professeur : Jean-Marc Beaulieu

Date : Le 5 février 2002

Durée : 1 heure 30 minutes

ELE-542-01 Système ordiné en temps réel

Examen mi-session

toute documentation permise • calculatrice autorisée

répondre à toutes les questions • remettre ce questionnaire avec votre cahier d’examen

Nom de l'étudiant(e) :

Code permanent :

Signature :

ELE-542 Systèmes ordinés en temps réel page 2 de 5

Question 1 (16 points) Concepts de base

Vous êtes responsable de concevoir un système qui doit gérer les signaux d’urgence provenant

de 3 capteurs de température. Dès que le processeur reçoit un signal d’un des capteurs, il doit

identifier ce capteur et entreprendre le plus rapidement possible l’exécution d’un sous-

programme d’urgence.

Un concept est proposé et vous devez l’analyser. Les principales caractéristiques du concept

proposé sont :

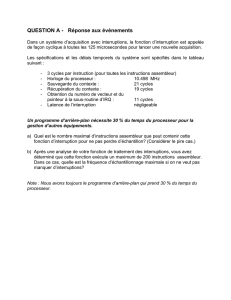

• L’architecture matérielle est illustrée dans le schéma ci-dessous.

• L’IRQ0 est utilisée par le processeur pour recevoir le signal, par interruption.

• L’identification du capteur est réalisée en interrogeant le registre d’état de chaque capteur

à tour de rôle.

• On suppose que IRQ0 est la plus prioritaire.

• On suppose qu’un seul capteur envoie un signal à la fois (pas de chevauchement des

interruptions).

a) Identifiez la principale faiblesse de ce concept au niveau du temps de réponse à un

événement. Justifier votre réponse [ou pourquoi est-ce une faiblesse?] (5 lignes maximum)

b) En conservant la même architecture matérielle que la figure ci-dessous, pouvez vous

proposer et justifier une méthode logicielle plus performante pour identifier le capteur qui

requiert l’attention du processeur ? Si oui, laquelle ? (5 lignes maximum)

CPU

Bus d’adresse et de données

IRQ7

IRQ0

Capteur 1

état

Capteur 2

état

Capteur 3

état

ELE-542 Systèmes ordinés en temps réel page 3 de 5

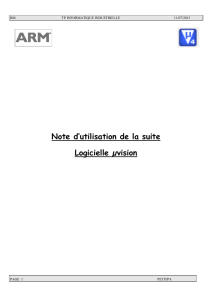

Question 2 (40 points) Réponse aux évènements

Dans un système d’acquisition avec interruptions, la fonction d’interruption est appelée de façon

cyclique à toutes les 200 microsecondes pour lancer une nouvelle acquisition.

Les spécifications et les délais temporels du système sont spécifiés dans le tableau suivant :

- 4 cycles par instruction (pour toutes les instructions assembleur)

- Horloge du processeur : 10.498 MHz

- Sauvegarde du contexte : 22 cycles

- Récupération du contexte : 24 cycles

- Obtention du numéro de vecteur et du

pointeur à la sous-routine d’IRQ : 17 cycles

- Latence de l’interruption négligeable

Un programme d’arrière-plan nécessite, à chaque acquisition, 40% du temps du processeur

pour le transfert de chaque échantillon vers le système d’affichage (par exemple, pour le

transfert du MC68332 vers le PC).

a) Quel est le nombre maximal d’instructions assembleur que peut contenir cette fonction

d’interruption pour ne pas perdre d’échantillon? (considérer le pire cas)

b) Après une analyse de votre fonction de traitement des interruptions, vous avez déterminé que

cette fonction exécute un maximum de 484 instructions assembleur. Dans ce cas, quelle est

la fréquence d’échantillonnage maximale si on ne veut pas manquer d’interruptions?

Note : Nous avons toujours le programme d’arrière-plan qui prend 40% du temps du

processeur.

ELE-542 Systèmes ordinés en temps réel page 4 de 5

Question 3 (24 points) Les aspects matériels – Vrai ou faux

Instructions :

• Indiquez si chacun des énoncés suivants est vrai ou faux.

• Lire attentivement les questions.

• Si vous répondez « faux », justifiez votre réponse, c’est-à-dire indiquez quelle partie de

l’énoncé est erronée. (5 lignes maximum)

a) Les entrés/sorties pilotées par interruptions offrent l’avantage d’améliorer le facteur

d’utilisation du processeur.

b) Le temps d’accès aux instructions est un facteur important pour la performance d’un

processeur.

c) Le registre IRR (Registre de requêtes d’interruptions) contient un bit actif (égale à 1) pour

chaque niveau d’interruption que le processeur à commencer à traiter.

d) Dans une architecture à pipeline, les branchements constituent une difficulté parce qu’il faut

vider tous les différents niveaux du pipeline avant de continuer.

e) Le processeur a toujours la priorité pour obtenir accès au bus de communication (bus de

données et bus d’adresse) même lorsque le système possède un contrôleur d’accès direct en

mémoire (DMA).

f) La méthode de traitement des interruptions par interrogation consiste à interroger le registre

d'état de chaque périphérique pour obtenir le vecteur d’interruption. Ce vecteur permet

ensuite d’identifier la fonction d’interruption à exécuter.

g) Les mémoires DRAM sont dites « dynamiques » parce qu’elles répondent très rapidement

aux requêtes du processeur.

h) Dans le micro-contrôleur Motorola MC68332, il faut exécuter une macro-instruction spéciale

pour accéder aux registres des différents modules spécialisés.

ELE-542 Systèmes ordinés en temps réel page 5 de 5

Question 4 ( 20 points)

Comme dans votre laboratoire, nous avons un système d’acquisition (ordinateur PC) qui reçoit

les échantillons sur le port série et qui affiche à l’écran le signal reçu dans le domaine temporel et

fréquentiel :

• Les échantillons sont reçus sur le port série à une fréquence constante qui est égale à la

fréquence d’échantillonnage.

• Chaque échantillon reçu par l’ordinateur PC requiert immédiatement 180 microsecondes

pour sa réception, son enregistrement dans le tampon et son affichage temporel.

• À tous les 256 échantillons reçus, l’ordinateur entreprend une transformée de Fourrier

discrète qui prend 8160 microsecondes, et l’affichage des résultats sous forme de spectre

de fréquence prend 800 microsecondes.

• On assume que l’ordinateur PC est dédié exclusivement à cette tâche (réception, affichage

temporel, transformée de Fourrier, affichage fréquentiel).

• On assume aussi que le port de communication série fonctionne à une vitesse suffisante

pour transmettre tous les échantillons. De plus, un tampon circulaire est disponible pour

enregistrer les données de façon temporaire durant les opérations de l’ordinateur PC.

En considérant les spécifications ci-dessus, quelle est la fréquence d’échantillonnage maximale,

en échantillon/sec, que peut supporter l’ordinateur PC pour éviter de perdre des échantillons ?

1

/

5

100%