DEVOIR 3 noté sur 5 points On considère l`architecture de

NFA004 – semestre 2 - 2012-2013

DEVOIR 3

1

DEVOIR 3 noté sur 5 points

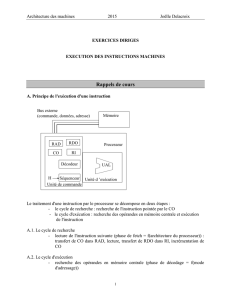

On considère l'architecture de processeur jointe. Les registres du processeur sont sur 32 bits. Les

portes à activer sont représentées par un rond sur la flèche.

Le format des microcommandes est :

- entrée du contenu d'un bus vers un registre : nombusnomregistreEn (exemple BR0En)

- sortie du contenu d'un registre vers un bus : nombusnomregistreSor (exemple

BCOSor)

- entrée sur une entrée de l'UAL@ : nombusentréeUAL@En ou

nomregistreentréeUAL@En (exemples RBUal@aEn, AUal@bEn)

- sortie des UAL : nombussortieUALSor et nombussortieUAL@Sor (exemple

BualsSor)

Le passage du bus A vers le bus B s'effectue en activant une opération Nop sur l'Unité

Arithmétique et Logique (UAL), ce qui a pour effet de copier le contenu de l’entrée a de l’UAL

sur la sortie de l'UAL. Ainsi pour passer le contenu du bus A au bus B, les étapes sont :

- mettre le contenu du bus A dans entrée a de l’UAL : AUalaEn ;

- activer l’opération Nop : Nop ;

- sortir la sortie de l’Ual sur la bus B : BualsSor.

L’opération de lecture et écriture est déclenchée par une micro-commande LEC ou ECR.

La micro-commande INCO incrémente le contenu du CO.

La micro-commande AXSor permet de sortir sur le bus A la partie basse du registre RI.

UAL

CO

R0

RDO

RAD

b

u

s

m

é

m

o

i

r

e

bus B

bus A

RB

RSP

Nop

add add

ab

s

a b

s

R1 R3 RI S Z O C

PSW

inco

UAL@

NFA004 – semestre 2 - 2012-2013

DEVOIR 3

2

Question 1 1,5 points

a/ Donnez la séquence de microcommandes associée à l'instruction ADD I R0 100 qui effectue

l’addition du registre R0 avec un mot mémoire obtenu par adressage indirect et stocke le résultat

dans R0. (1 point)

b/ Le processeur représente les entiers signés en complément à 2 sur 16 bits. Lors de l’exécution

de l’instruction ADD I R0 100, le registre R0 contient la valeur (+ 32750)

10

. La mémoire centrale

contient entre autre les données suivantes

Adresse mémoire Contenu du mot

100 150

150 30

Quel est le résultat de l’opération réalisée ? Comment cela se traduit-il au niveau de l’unité

arithmétique et logique ? (0,5 point)

Question 2 1,25 points

Le processeur dispose d’une mémoire cache associative de 4 entrées. Les adresses mémoire sont

sur 16 bits. Chaque mot mémoire fait 32 bits. La mémoire centrale est adressable par octet.

Chaque entrée du cache contient un bloc de 4 mots.

a/ Quelle est la taille de l’étiquette ? (0,25 point)

b/ Soit la suite de références suivantes, qui correspondent aux accès mémoire demandés

par le processeur, en terme d’adresses d’octets, dans le temps. Les adresses sont données en

hexadécimal (base 16)

temps 0 1 2 3 4 5 6 7 8

adresse 001F 0A1F 013A 001D 1B1E 0014 013B 1B32 1137

En utilisant l’annexe fournie sur laquelle vous reporterez votre numéro de copie, donnez

l’évolution des 4 entrées du répertoire du cache et notez les défauts dans les deux cas suivants

1/ la politique de remplacement est FIFO (0,5 point)

2/ la politique de remplacement est LRU. (0,5 point)

Question 3 (1,25 point)

Le processeur dispose à présent d’une mémoire cache à correspondance directe de 4 entrées. Les

adresses mémoire sont sur 16 bits. Chaque mot mémoire fait 32 bits. La mémoire centrale est

adressable par octet. Chaque entrée du cache contient un bloc de 4 mots.

a/ Quelle est la capacité de la mémoire centrale exprimées en Ko (0,25 point)

b/ Quelle est la taille de l’étiquette ? (0,5 point)

c/ Quelle est la taille réelle du cache ? (0,5 point)

NFA004 – semestre 2 - 2012-2013

DEVOIR 3

3

Question 4 (1 point)

On considère une machine admettant 8 niveaux d’interruptions matérielles numérotées de 0 à 7,

le niveau d’interruptions 0 étant le plus prioritaire et le niveau 7 le moins prioritaire. Le

processeur dispose de deux broches, une broche INT sur laquelle lui parvient le signal

d’interruption, une broche INTA avec laquelle il acquitte les interruptions. Les 8 niveaux

d’interruptions sont gérés par un contrôleur d’interruptions. Il ne vous est pas demandé de donner

l’évolution des registres du contrôleur.

a) A l’instant 0, le contrôleur d’interruption reçoit les interruptions 7, 4, 5. Quelle interruption est

délivrée au processeur ? Que fait le processeur ? (0,5 point)

b) Durant le traitement par le processeur de l’interruption délivrée selon vous à la question a, le

contrôleur reçoit l’interruption 2. Que se passe-t-il ? Aucune autre interruption n’est délivrée au

contrôleur. Donnez l’ordre de service de ces interruptions par le processeur. (0,5 point)

NFA004 – semestre 2 - 2012-2013

DEVOIR 3

4

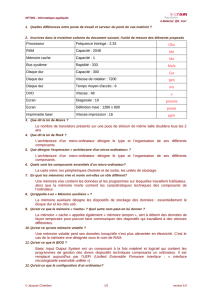

ANNEXE

NOM Prénom :

1/ Remplacement FIFO

temps 0 1 2 3 4 5 6 7 8

adresse 001F 0A1F 013A 001D 1B1E 0014 013B 1B32 1137

Ligne 1

Ligne 2

Ligne 3

Ligne 4

Défaut/

Succès

2/ Remplacement LRU

temps 0 1 2 3 4 5 6 7 8

adresse 001F 0A1F 013A 001D 1B1E 0014 013B 1B32 1137

Ligne 1

Ligne 2

Ligne 3

Ligne 4

Défaut/

Succès

1

/

4

100%