A.2(1)

GPA770: Microélectronique appliquée Éric Granger A.2-1

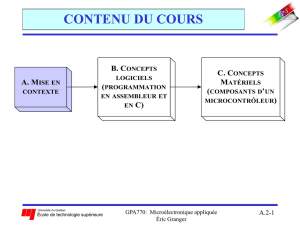

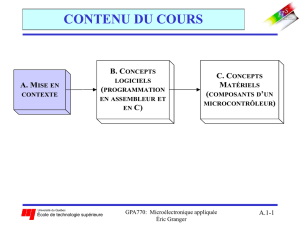

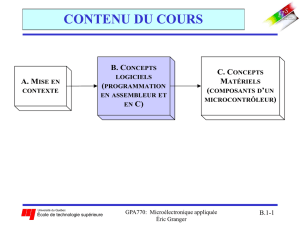

CONTENU DU COURS

GPA770: Microélectronique appliquée Éric Granger A.2-2

Partie A − Mise en contexte

A.1 Survol de l’électronique numérique

–systèmes de numérotation

–opérations arithmétiques binaires

–représentation de nombres signés

–circuits électroniques de base: portes, registres, etc.

A.2 Architecture et programmation du 68HC12:

–systèmes électroniques universels

–architecture, sous-systèmes et mémoires

– instructions et modèle du programmeur

GPA770: Microélectronique appliquée Éric Granger A.2-3

Sommaire de la Section A.2

A.2 Architecture et programmation du 68HC12:

1) Systèmes électroniques universels

2) Architecture, sous-systèmes et mémoires

3) Instructions et modèle du programmeur

GPA770: Microélectronique appliquée Éric Granger A.1-4

A.1(5) Systèmes électroniques universels

a. Système numérique

déf.: un système composé de registres et de portes

logiques contrôlées par un circuit séquentiel synchrone

Structure: unité de contrôle + logique de traitement

Avantage et inconvénients de l’approche:

−donne généralement un système moins complexe

−plus facile à concevoir, changer et réparer le matériel

−mais, peut être plus lent qu’un circuit dédié

GPA770: Microélectronique appliquée Éric Granger A.1-5

A.1(5) Systèmes électroniques universels

Exemple: périphérique SPI pour la communication

sérielle synchrone

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

1

/

34

100%