B.1(1)

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger B.1-1

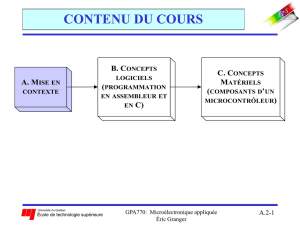

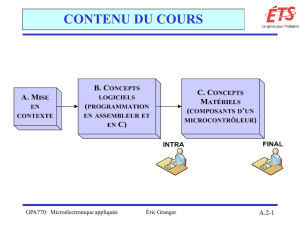

CONTENU DU COURS

A. MISE EN

CONTEXTE

B. CONCEPTS

LOGICIELS

(PROGRAMMATION

EN ASSEMBLEUR ET

EN C)

C. CONCEPTS

MATÉRIELS

(COMPOSANTS D’UN

MICROCONTRÔLEUR)

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger B.1-2

Partie B − Concepts logiciels

B.1 Langage assembleur et programmation structurée:

modes d’adressage et jeu d’instructions

boucles, pile et sous-routines

programmation structurée

B.2 Microcontrôleurs à logique floue:

systèmes de contrôle à logique floue

Instructions spécialisées du 68HC12

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger B.1-3

Sommaire de la Section B.1

B.1 Langage assembleur et programmation

structurée:

1) Processus d’assemblage

2) Directives de compilation

3) Modes d’adressage

4) Jeu d’instructions

5) Boucles

6) Piles

7) Sous-routines: appel et passage de paramètres

8) Sous-routines utilitaires du D-BUG12

9) Programmation structurée

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger B.1-4

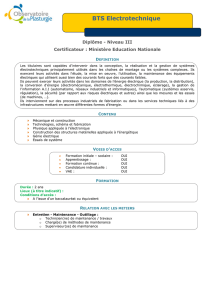

B.1(1) Processus d’assemblage

Le processus génère:

1. un fichier en langage machine (*.s19): selon le format

de Motorola

2. un fichier liste (*.lst): pour le déverminage:

–affiche le code machine pour chaque adresse

mémoire

– indique l’adresse d’exécution et le mode d’opération

de chaque instruction

code source en

langage assembleur code assemblé en

langage machine

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger B.1-5

B.1(1) Processus d’assemblage

MODIFICATIONS AU

PROGRAMME ASSEMBLEUR

PROGRAMME

ASSEMBLEUR

(fichier.asm)

PROGRAMME EN

LANGUAGE MACHINE

(fichier.s19)

LISTING DU PROGRAMME

(fichier.lst)

ASSEMBLEUR

EXÉCUTION SUR

LE 68HC12

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

1

/

55

100%