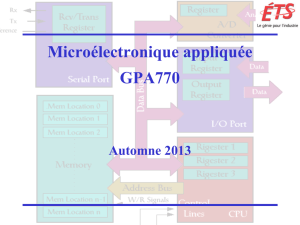

COURS GPA

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger A.2-1

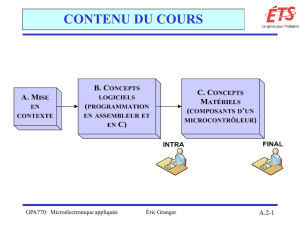

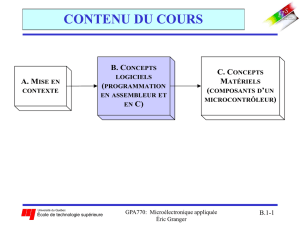

CONTENU DU COURS

A. MISE EN

CONTEXTE

B. CONCEPTS

LOGICIELS

(PROGRAMMATION

EN ASSEMBLEUR ET

EN C)

C. CONCEPTS

MATÉRIELS

(COMPOSANTS D’UN

MICROCONTRÔLEUR)

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger A.2-2

Partie A − Mise en contexte

A.1 Survol de l’électronique numérique

systèmes de numérotation

opérations arithmétiques binaires

représentation de nombres signés

circuits électroniques de base: portes, registres, etc.

systèmes électroniques universels

A.2 Architecture et programmation du 68HC12:

architecture, sous-systèmes et mémoires

modèle du programmeur et exécution d’instructions

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger A.2-3

Sommaire de la Section A.2

A.2 Architecture et programmation du 68HC12:

1) Architecture, sous-systèmes et mémoires

2) Instructions du 68HC12

3) Modèle du programmeur

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger A.2-4

A.2(1) Architecture, sous-systèmes et mémoires

Introduction du 68HC12 au marché en 1997:

évolution direct du 68HC11 qui est plus performante

et versatile (instructions, modes d’adressage, etc.)

Microcontrôleur avec CPU à 16 bits: le chemin de

données interne est de 16 bits

horloge de système à 8 MHz: générée par un crystal à

16MHz divisé par 2

conçu en technologie CMOS: la consommation de

puissance est basse

système = {modules} connectés à un bus inter module

(LIM)

Université du Québec

École de technologie supérieure GPA770: Microélectronique appliquée

Éric Granger A.2-5

A.2(1) Architecture, sous-systèmes et mémoires

Évolution du 68HC12:

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%