Amplificateurs opérationnels I – La paire différentielle.

1

Amplificateurs opérationnels

I – La paire différentielle.

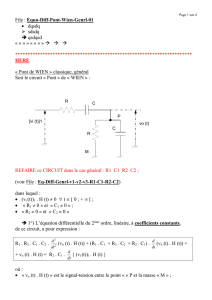

1 – Introduction – notion de signal différentiel.

Paire différentielle : parmi les briques de base les plus

importantes de l’électronique.

Un signal électrique est généralement mesuré par rapport à la masse

(c.-à-d. un potentiel fixe) :

vE

Z

vS

t

vS

Intérêt : - grande immunité au bruit et aux interférences,

- facilité de polarisation,

- meilleur linéarité.

2

I – La paire différentielle

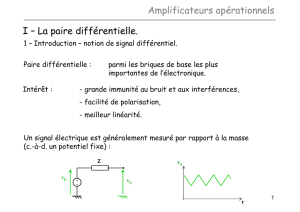

Un signal différentiel est mesuré entre deux nœuds ayant des

excursions de tension égales et opposées par rapport à un potentiel

fixe (le mode commun) :

vE1

Z

vS1 vE2

Z

vS2

vDIFF

vDIFF = vS1 – vS2

t

vS1

VS

mode

commun

t

vS2

VS

t

vDIFF

ΔV

2ΔV

ΔV

de plus vS1 + vS2 = 2VS

3

I – La paire différentielle

2 – La paire différentielle MOS.

a. Présentation.

I0

VDD

RD RD

Mn1 Mn2

vD1 vD2

vG1 vG2

iD1

iD2

Mn1 et Mn2 sont identiques

Axe de symétrie vertical

Polarisation par une source

de courant idéale (r0= ∞)

et polarisés en régime saturé.

4

I0

VDD

RD RD

Mn1 Mn2

vD1 vD2

vG1 vG2

iD1

iD2

I – La paire différentielle

Analogie paire différentielle – balance à deux fléaux.

5

I – La paire différentielle

b. Fonctionnement avec une tension d’entrée en mode commun.

⇒ vG1 = vG2 = vCM

I0

VDD

RD RD

Mn1 Mn2

vD1 vD2

vS

I0/2

VGS VGS

I0/2

D’après Mn1 et Mn2 identiques et par

considérations de symétrie :

vCM

iD1 = iD2= I0/2

On a vS = vCM – VGS tel que :

soit :

vDIFF

Au niveau des drains :

la tension différentielle de sortie :

vDIFF = vD2 – vD1 = 0

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

1

/

29

100%