Circuits Intégrés Analogiques - 2012/2013 - Chapitre I 11/03

Circuits Intégrés Analogiques

- 2012/2013 - Chapitre I

11/03/2013

1

M2 EEA – Systèmes Microélectroniques

Polytech’montpellier – ERII 3

Circuits Intégrés Analogiques

Chapitre I

Rappels, Modélisation et Simulation de transistors MOS

Pascal Nouet / 2012-2013

http://www2.lirmm.fr/~nouet/homepage/lecture_ressources.html

Téléchargement des supports

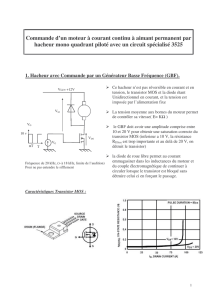

• Initiation aux circuits intégrés analogiques

– 6h cours / 18h de TD-TP / 24h de travail personnel

– Maitrise du transistor MOS en régime de saturation

– Montage élémentaires à base de MOST saturés

• Sources de courants – Amplificateurs à un

transistor

– Utilisation du logiciel Cadence-Virtuoso

• Téléchargement des supports

– Support de cours – Tuto Cadence

– http://www2.lirmm.fr/~nouet/homepage/lecture_res

sources.html

Contenu du cours

• Chapitre I : Rappels, Modélisation et Simulation

de transistors MOS

– Physique du composant

– Modèles grand et petit-signal du MOS

– Premier pas en simulation électrique de transistors

MOS dans l’environnement Cadence-Virtuoso

Circuits Intégrés Analogiques

- 2012/2013 - Chapitre I

11/03/2013

2

Plan

• Rappels de physique du composant

– Silicium monocristallin

– Jonction PN

– Transistor MOS

• Modélisation BF du transistor MOS

• Simulation électrique

Silicium monocristallin

• Intrinsèque (nn= np)

• Densité double chaque fois que la température

augmente de 11°C

• Dopage Phosphore ou Arsenic (ND, cm-3)

électrons libres en excès

charge négative ou donneurs

type N

• Dopage Bore (NA, cm-3)

trous libres en excès

charge positive ou accepteurs

type P

300K @ mporteurs/c 105,1

310

⋅=

i

n

D

i

n

N

n

p

2

=

A

i

p

N

n

n

2

=

Silicium monocristallin

• Résistivité du silicium

– Dépends de la mobilité des

porteurs et de leur densité

– Dans le cas du silicium intrinsèque (nn=np=ni), la

résistivité est très élevée, le silicium est isolant

– Lorsque le silicium est dopé la densité de porteurs

dans le silicium augmente drastiquement et la

résistivité ne dépend que des porteurs majoritaires.

– Rem. 1 : la mobilité s’exprime en cm2/(V.s)

– Rem. 2 : la résistivité obtenue est en Ω.cm (1C=1A.s)

( )

ppnn

nnq

µµ

ρ

+

=1

Dnnn

n

Nqnq

µµ

ρ

11 ==

Appp

p

Nqnq

µµ

ρ

11 ==

Circuits Intégrés Analogiques

- 2012/2013 - Chapitre I

11/03/2013

3

Silicium monocristallin

• Résistance d’un barreau

de silicium dopé

• Au final, cette résistance dépend des

dimensions horizontales (W,L), de la mobilité et

de la densité surfacique de charge dans le

barreau Qn(C/cm2)

eqNQavec

L

W

Q

eW

L

NqeW

L

R

DAn

nnp

DAnp ,

,

,,

1

.

1

.====

µ

µ

ρ

LW

e

Jonction PN

• Diode non polarisée

– diffusion d’un trou vers la zone N

recombinaison avec un électron libre charge +

– diffusion d’un électron vers la zone P

recombinaison avec un trou libre charge -

– Apparition d’une différence de potentiel et d’un

champ électrique s’opposant à la diffusion

Potentiel de Jonction

=Φ

2

0

ln

i

DA

nNN

q

kT

Jonction PN

• Largeur de la zone de déplétion

– Cas d’une diode P+N (NA>>ND)

– Cas d’une diode N+P (ND>>NA)

– Effet d’une polarisation inverse

• S’ajoute au potentiel de jonction

• Augmente la largeur des zones de déplétion

Φ0est remplacé par Vr+ Φ0

( )

DAD

A

r

n

NNN N

q

X+

Φ

≅

00

2

ε

ε

( )

DAA

D

r

p

NNN N

q

X+

Φ

≅

00

2

ε

ε

Circuits Intégrés Analogiques

- 2012/2013 - Chapitre I

11/03/2013

4

Transistor MOS (e.g. canal N)

• Principe

– Rendre passant un transistor MOS N consiste à faire

apparaitre une jonction N+P verticale sous la grille.

Pour cela on applique une polarisation positive sur la

grille par rapport au substrat.

Transistor MOS (e.g. canal N)

• Tension de seuil (1/2)

– L’accumulation de charges négatives sous la grille fait

tout d’abord apparaître une zone intrinsèque

(ND=NA=ni) dont le potentiel de travail est :

– On considère que le canal est établi (zone N+ sous la

grille) lorsque l’on atteint le régime de forte inversion

ce qui corresponds à un potentiel de travail

2.φ

f

pour

la jonction N+P ainsi obtenue.

( )

==Φ=

i

A

iDf

n

N

q

kT

nN ln

0

φ

Transistor MOS (e.g. canal N)

• Tension de seuil (2/2)

– La zone de déplétion est majoritairement dans le

substrat P et l’on peut calculer sa largeur :

– La quantité de charge

accumulée sous la grille

est alors :

– La tension

V

gs

nécessaire pour

atteindre cet état d’équilibre

est la tension de seuil :

( )

A

fr

ADp

qN

NNXW

φεε

0

4

≅>>=

(

)

frAAox

qNWqNcmCQ

φεε

0

2

4/ ≅=

f

ox

ox

ttn

C

Q

VV

φ

2

0

+==

Circuits Intégrés Analogiques

- 2012/2013 - Chapitre I

11/03/2013

5

Transistor MOS (e.g. canal N)

• Fonctionnement du MOS

– Bloqué

– Passant

0

<

−

tngs

V

V

0

>

−

tngs

V

V

Transistor MOS (e.g. canal N)

• Régimes de fonctionnement

– Le transistor MOS

en régime linéaire

dstngsdstngs

V

V

V

V

V

V

>

−

>

>

−

et

0

;

0

( )

dstngsoxnds

VVV

L

W

CµI ⋅−=

( )

⇒−==

tngsoxn

nn

ds

VVCQavec

L

W

Q

R

1

µ

Transistor MOS (e.g. canal N)

• Régimes de fonctionnement

– Le transistor MOS en

régime saturé

dstngsdstngs

V

V

V

V

V

V

<

−

>

>

−

et

0

;

0

(

)

tngseffeff

oxn

tngs

oxn

dsat

VVVV

L

WCµ

VV

L

WCµ

I−==−= avec

2

2

22

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

1

/

22

100%