Processeurs embarqués spécifiques et production de code (Charot)

n

n

n

n

n

n

n

n

1

1

Ecole thématique Seix - Novembre 2000 - F. Charot 1

Processeurs embarqués spécifiques

Processeurs embarqués spécifiques

et production de code

et production de code

François Charot

Irisa/Inria

Rennes

Ecole thématique Seix - Novembre 2000 - F. Charot 2

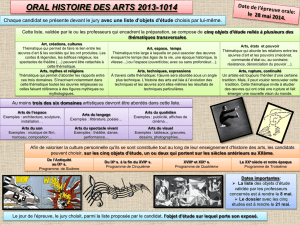

Plan de la présentation

nQuelques aspects concernant la production

de logiciel pour les systèmes enfouis

nCompilateurs pour processeurs embarqués

nCompilateurs reciblables

nApproche ARMOR/CALIFE

nConclusion

n

n

n

n

n

n

n

n

2

2

Ecole thématique Seix - Novembre 2000 - F. Charot 3

Plan de la présentation

n

nQuelques aspects concernant la production

Quelques aspects concernant la production

de logiciel pour les systèmes enfouis

de logiciel pour les systèmes enfouis

Types de processeurs

Types de processeurs

codesign

codesign matériel/logiciel

matériel/logiciel

outils de spécification de systèmes

outils de spécification de systèmes

nCompilateurs pour processeurs embarqués

nCompilateurs reciblables

nApproche ARMOR/CALIFE

nConclusion

Ecole thématique Seix - Novembre 2000 - F. Charot 4

Logiciels et processeurs embarqués

nRévolution technique des applications grand public

du type multimédia, télécoms

•Technologies d’intégration

•Outils de conception

*

*système sur silicium, système

système sur silicium, système mono

mono-puce

-puce

nLa loi du time to market impose réaction rapide et

anticipation stratégique

*

*emploi du logiciel et intégration de cœurs de

emploi du logiciel et intégration de cœurs de

processeurs (temps de conception raisonnable)

processeurs (temps de conception raisonnable)

•flexibilité en terme de conception

•flexibilité en terme d’évolution

n

n

n

n

n

n

n

n

3

3

Ecole thématique Seix - Novembre 2000 - F. Charot 5

Caractéristiques

d’un processeur embarqué

nCœur de processeur

•partie centrale d’un processeur (plus périphériques)

nContrainte de performance

•notion de temps réel

nProblème de la densité de code : taille du code

applicatif (mémoire)

•la mémoire tend à occuper la majeure partie d’une

puce

•impact de la taille du cœur dans le choix du

processeur

Ecole thématique Seix - Novembre 2000 - F. Charot 6

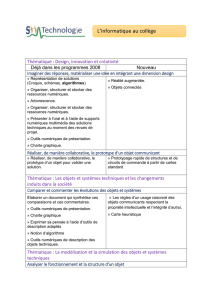

Styles architecturaux

des processeurs embarqués

micro

contrôleur

spécifique

ASIP

DSP

VLIW

RISC

n

n

n

n

n

n

n

n

4

4

Ecole thématique Seix - Novembre 2000 - F. Charot 7

Caractéristiques

d’un logiciel embarqué

nTaille réduite de programme

quelques centaines, voire milliers de lignes de code C

nGestion simplifiée de la mémoire

absence d’allocation dynamique

nGestion simplifiée des entrées/sorties (flot de

donnée)

nExécution cyclique rythmée par le flot de

données

nContraintes temporelles fortes

*

* Ces caractéristiques influent sur la compilation

Ces caractéristiques influent sur la compilation

Ecole thématique Seix - Novembre 2000 - F. Charot 8

Caractéristiques

d’un logiciel embarqué (suite)

nHistoriquement, emploi de l’assembleur

•notamment pour les parties critiques

n Aujourd ’hui, des langages de haut niveau

comme C, C++ s ’imposent

•augmentation de complexité

•portabilité

•progrès de la technologie de compilation

•évolution des architectures

n

n

n

n

n

n

n

n

5

5

Ecole thématique Seix - Novembre 2000 - F. Charot 9

Caractéristiques

d’un logiciel embarqué (suite)

nImpact du style d’écriture du code sur les

performances

•niveau comportemental (norme C ANSI)

usage de constructions de haut niveau (tableaux,

structures)

•second niveau

utilisation de pointeurs, de fonctions prédéfinies

•troisième niveau

assignation manuelle de variables à des registres de

l’architecture cible (directives)

•quatrième niveau

mélange de C bas niveau avec directives et d’assembleur

Lisibilité

Lisibilité

portabilité

portabilité

efficacité

efficacité

Ecole thématique Seix - Novembre 2000 - F. Charot 10

Compilation de programmes embarqués

nRôle essentiel du compilateur

•générer rapidement des programmes efficaces

•importance de l’optimisation de code

–taille de code

–vitesse d’exécution

–puissance ou énergie consommée

nAutomatiser la conception du compilateur

*

*Compilation

Compilation reciblable

reciblable

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

1

/

40

100%