Conception d`un amplificateur sélectif à transistor

le transistor bipolaire en amplification- Amplificateur sélectif LC 3MIC_BE T'com

Conception d'un amplificateur sélectif à transistor

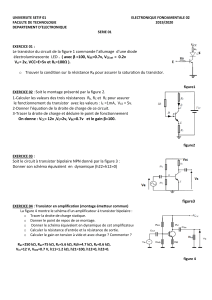

Schéma proposé :

Vcc = 12V.

R, L et C sont les éléments calculés au TD précédent.

Transistor : Vbe=0,6V ; uT = 25 mV ;

β

= 100.

1. Redessiner ce circuit en polarisation

(fréquence nulle).

2. En déduire les expressions de :

- Vc0

- Vb0 en supposant que ib est négligeable

- Ve0 en fonction de Vb0

- Ie0 (= Ic0)

3. Faire le schéma équivalent dynamique à la

fréquence de résonance. CE et CL1 seront choisis

de manière à être considérés comme des court-

circuits dynamiques, à la fréquence considérée.

4. On veut en sortie une dynamique de 8 Vpp. Calculer l'amplitude du courant dynamique ic.

5. Sachant que le transistor a une tension de saturation Vcesat de 0,2V, déterminer la valeur

maximale de la tension Ve0 que l'on peut choisir. En déduire Vb0. Le tracé de Vs(t) (polarisation +

dynamique) pourra être très utile.

6. Le courant Ic = Ic0 + ic, doit toujours être positif, sans quoi, T se bloque. En déduire le courant

minimum à choisir pour Ic0.

7. Dimensionner tous les éléments du montage.

8. Calculer le gain du montage.

9. On veut diminuer ce gain et l'amener à 26dB. Pour cela, la solution est de placer en série avec CE

une résistance R3. Faire le nouveau schéma équivalent dynamique. Montrer alors que

l'amplification vs/e # R/R3. Calculer R3.

Vérification expérimentale:

Procéder à la simulation de votre circuit sans contre-réaction (R3 = 0). Vérifier la conformité du

filtre par une analyse AC.

Vérifier les caractéristiques temporelles (dynamique de sortie) par une analyse transitoire.

Réaliser le montage sur plaque d'essais. Valider la solution expérimentalement.

Faire de même pour le montage amplificateur contre-réactionné (gain de 26dB).

BE_Transistor_v3.pdf 2006-2007 1/1

Vs

Vcc

eV0

Ib IC

RE

CE

CL1

R1

R2

T

C

R

L

1

/

1

100%