CEM des Circuits Intégrés

ENSEEIHT

Département Electronique et Génie Electrique par la voie de

l'Apprentissage

Octobre 2013

CEM des

Circuits

Intégrés

Bureau d’étude –

Développement d’un

modèle ICEM d’un

microcontrôleur

Alexandre Boyer, Etienne Sicard

2

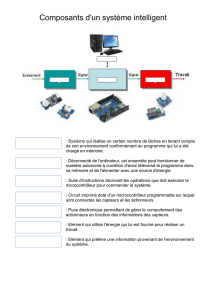

I. Enoncé du projet

Le dsPIC 33F est un microcontrôleur 16 bits dédié à des applications de traitement de signal. Les

caractéristiques de ce composant sont données de l’annexe A. Ce composant va être utilisé pour

diverses applications embarquées. Afin d’assurer leur sûreté de fonctionnement, ce composant doit

présenter des niveaux d’émission électromagnétique réduits. Vos clients sont de plus en plus

demandeurs de modèles ICEM de circuits intégrés, leur permettant d’anticiper par simulation le

niveau d’émission conduite ou rayonnée de leur application (schéma du processus de simulation du

client utilisant ICEM) et de valider ou modifier la conception de leur application (placement-routage,

découplage, filtrage, choix de composants).

Votre mission est de développer un modèle ICEM du dsPIC 33F. Celui-ci doit être permettre une

simulation de l’émission conduite entre 1 MHz et 1 GHz. Ce modèle doit être un schéma électrique

compatible SPICE (WinSPICE).

Pour créer votre modèle, vous disposez d’un ensemble de mesures effectuées par votre laboratoire

CEM. L’annexe C fournit les détails de chaque mesure. Votre modèle doit valider les mesures

suivantes :

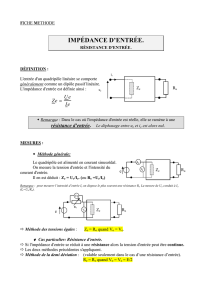

Mesures d’impédance entre les broches d’alimentation du composant

Mesures d’impédance du plan d’alimentation de la carte de test

Mesures de courant (sonde 1 ohm) dans différents modes de fonctionnement

Mesure de la forme temporelle du signal en sortie d’un pad d’I/O

Les logiciels IC-EMC et WinSPICE seront utilisés pour les différentes étapes de construction du

modèle. A l’issue du projet, on vous demande de :

fournir les schématiques décrivant le modèle ICEM du composant

fournir un rapport détaillant la construction des modèles, les validant et donnant leur

précision

3

II. Annexe A – Données sur le dsPIC 33F

Le dsPIC est un microcontrôleur 16 bits, dédié au traitement de signal. Il existe en différentes

versions de boîtier, celui que vous allez utiliser est monté dans un boîtier QFP 64 (version

dsPIC33FJ128GP706). Ce microcontrôleur embarque un grand nombre de périphériques, que nous ne

détaillerons pas ici. L’horloge système est limitée à 40 MHz. Dans notre application, celle-ci sera

produite par un oscillateur interne. La tension d’alimentation nominale du composant est de 3.3 V.

Celle-ci est fournie aux différents blocs par plusieurs paires d’alimentation :

4 broches Vdd et 3 broches Vss dédiées à l’alimentation des pads d’I/O et des blocs digitaux

internes du microcontrôleur

AVdd/AVss dédiée à l’alimentation des blocs analogiques

Brochage du circuit

Configuration du composant lors des mesures CEM

Lors des mesures CEM effectuées sur le composant, celui-ci était dans la configuration suivante :

L’horloge système est fixée à 20 MHz, elle est produite par l’oscillateur et la PLL interne qui

fonctionne à 40 MHz.

Le programme embarqué dans le microcontrôleur permet soit de n’activer aucun pad

d’entrée-sortie (activité minimale), soit activer un pad d’entrée-sortie (pad RB0), soit

d’activer simultanément 16 pads d’entrée-sortie (pads RB0 à RB15). La fréquence de

commutation des pads d’entrée-sortie est de 5.7 MHz.

4

Annexe B – Données sur le circuit imprimé

La carte de circuit imprimé construite pour réaliser les différentes mesures pour la construction du

modèle ICEM présente les dimensions suivantes : 100 × 100 mm (photo ci-dessous). Elle est

construite en FR4 6 couches. Ci-dessous, une description de l’empilement des 6 couches. Le dsPIC est

monté sur la face TOP de la carte.

Top layer (1)

Bottom layer (6)

Couches

Signaux

Type

Epaisseur

(mm)

Conductivité /

tangente de pertes

Constante

diélectrique

(1) – Top

Ground +

Signal

Cuivre

0.035

57 ×106 S / _

_

Diélectrique

FR4

0.21

_ / 0.02

4.5

(2)

Signal

Cuivre

0.018

57 ×106 S / _

_

Diélectrique

FR4

0.36

_ / 0.02

4.5

(3) - GND

Ground

Cuivre

0.018

57 ×106 S / _

_

Diélectrique

FR4

0.2

_ / 0.02

4.5

(4) POWER

Vdd_3.3V

Cuivre

0.018

57 ×106 S / _

_

Diélectrique

FR4

0.36

_ / 0.02

4.5

(5)

Signal

Cuivre

0.018

57 ×106 S / _

_

Diélectrique

FR4

0.21

_ / 0.02

4.5

(6) -

BOTTOM

Signal +

Ground

Cuivre

0.035

57 ×106 S / _

_

Schématique de la carte :

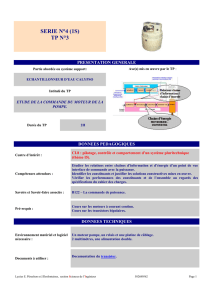

La figure ci-dessous détaille le schéma électrique de la carte de test sur laquelle est montée le dsPIC

33F et sont réalisées les essais CEM. Une mémoire externe SRAM est connectée au microcontrôleur.

Celle-ci n’est pas active lors des essais CEM. Tous ces pads d’I/O sont configurés en entrée et servent

de charge pour les pads d’I/O du microcontrôleur. La capacité d’entrée d’un pad d’I/O de la mémoire

est de 10 pF. Les pistes connectant les entrées des mémoires au sortie du microcontrôleur sont de

5

type ligne microruban, de largeur égale à 0.6 mm et placée à 0.6 mm du plan de masse. On pourra

supposer que la charge connectée à chaque pad de sortie du microcontrôleur est de l’ordre de 20 pF.

Lors des tests, l’alimentation 3.3 V a été directement fournie par le connecteur J1 qui permet l’accès

direct au plan d’alimentation Vdd_3.3V. Des mesures à l’analyseur de réseau pour caractériser

l’impédance de ce plan d’alimentation ont été effectuées depuis ce connecteur.

Quatre condensateurs céramiques de découplage de 100 nF sont montés entre les plans Vdd_3.3V et

le plan de masse GND. Elles sont de type X7R 50 V, tolérance de 10 %, montées en boîtier 0603. Le

fabricant donne une valeur de résistance série ESR de 70 mΩ et d’inductance série ESL de 1.5 nH.

Le connecteur J2 est placé en parallèle d’une résistance de 1 Ω, connectée à l’ensemble des broches

Vss du microcontrôleur. La tension à ses bornes est proportionnelle au courant sortant par les

broches Vss du dsPIC 33F et permet de caractériser l’émission conduite.

Microcontroller

dsPIC 33F

SRAM

Memory

Pad D0

J2 - dsPIC

1 Ωprobe

J1 - Direct access to

Vdd_3.3V plane

6

6

1

/

6

100%