Amplificateur Source Commune CMOS : Exercices et Simulations

Faculté des Sciences, UM2 GMEE102 2011/2012

Yves BERTRAND (bertrand@lirmm.fr) 1 11/12/2011

Amplificateur source commune

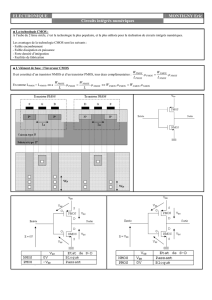

Soit la cellule CMOS donnée ci-dessous.

Données concepteur :

• Largeur des transistors M

1

et M

2

: W

1

=W

2

=100µm ;

• Tous les transistors sont à la longueur minimale L=L

min

=10µm ;

• V

DD

=5V.

Paramètres fondeur :

• NMOS : VTO=1V ; KP=20e-6 ; LAMBDA=0.01 ; TOX=200e-10 ; CGDO=200e-12 ;

CGSO=200e-12

• PMOS : VTO=-1V ; KP=10e-6 ; LAMBDA =0.01 ; TOX=200e-10 ; CGDO=200e-12 ;

CGSO=200e-12

v

i

v

o

V

DD

M

1

M

2

M

3

M

4

A

1 / Polarisation

a) Dimensionnez les transistors M

3

et M

4

de façon à polariser le point A à 3V.

Aide à la résolution : M

3

et M

4

ne servent qu'à assurer la polarisation de la grille de M

2

à

la valeur souhaitée. Pour déterminer le rapport des largeurs W

3

/W

4

des transistors, il faut

égaler les expressions des courants des deux transistors. La relation liant V

DD

et les V

GS

des transistors donne une seconde équation qui, combinée à la première, permet de

trouvez la valeur du rapport W

3

/W

4

. Sachant que la plus petite dimension possible pour un

W est donnée par la dimension L

min

du fondeur et sachant que l'on cherche à minimiser la

surface de silicium, on en déduit les valeurs numériques de W

3

et W

4

.

b) Calculez les courants qui parcourent tous les transistors du montage.

c) Calculez la tension continue à appliquer sur la grille de M

1

pour positionner la sortie V

o

à

V

DD

/2, en régime continu.

d) Calculez les paramètres g

m

et g

o

des quatre transistors.

e) Simulation : Implantez le circuit sous pspice, simulez-le et vérifiez toutes les valeurs de

polarisation précédemment calculées

2 / Régime dynamique

a) Donnez le schéma équivalent basses fréquences de la cellule.

Aide à la résolution : en régime dynamique, seuls les transistors de la cellule

amplificatrice doivent être modélisés.

b) Calculez la résistance de sortie R

out

de cette cellule. Calculez son gain en tension A

V

=v

o

/v

i

.

c) Simulation : Implantez le circuit sous pspice et simulez le. Utilisez la commande ".dc"

pour tracer la caractéristique (tension de sortie)/(tension d'entrée). Vérifiez le bon

Faculté des Sciences, UM2 GMEE102 2011/2012

Yves BERTRAND (bertrand@lirmm.fr) 2 11/12/2011

positionnement de la valeur de polarisation d'entrée calculée (question 1.c) sur cette

caractéristique. Utilisez la commande ".tf" pour déterminer les valeurs simulées de A

V

et

R

out

. Commentez.

3 / Etude en fréquence

a) Calculez la valeur des capacités parasites qui interviennent dans le modèle en fréquence

des transistors.

Aide à la résolution : le calcul se fait à partir des données fondeurs et des dimensions des

transistors (cellule de base seulement)

b) Donnez le schéma dynamique en fréquence (avec prise en compte des capacités parasites

des transistors) en prenant en compte l'existence d'une source de tension petit signal v

s

d'impédance R

s

=100kΩ connectée sur l'entrée du montage.

c) Retrouver les expressions du cours pour les fréquence des pôles f

1

, f

2

et du zéro f

z

.

d) A partir de ces expressions (non simplifiées) calculez la fréquence des pôles et du zéro.

e) Simulation : Implanter le circuit sous spice et tracez le diagramme de Bode en gain et en

phase. Commentez.

Aide à la simulation : il faut appliquer sur l'entrée un signal variable superposé à la valeur

de polarisation. Pour ce faire vous pouvez utilisez un montage du même type que celui vu

en cours pour l'étude en fréquence de la cellule amplificatrice CMOS à source commune et

charge GD-MOS (exemple d'application). Utilisez les valeurs suivantes : R

s

=100k

Ω

;

C

bias

=10

µ

F ; R

bias

=1M

Ω

; V

bias

= "la valeur calculée dans la question 1".

La syntaxe des lignes de code pspice à utiliser pour l'analyse ac est la suivante :

* source de tension sinusoidale pour etude en frequence (Bode)

* attention : n'utilisez pas d'accent dans les commentaires

vin noeud1 noeud2 ac 1

* analyse ac pour trace du diagramme de Bode, pour des frequences allant

* de fstart a fstop en prenant nbpoints par decade

.ac dec nbpoints fstart fstop

* lancement de l'outil de visualisation des courbes

.probe

Faculté des Sciences, UM2 GMEE102 2011/2012

Yves BERTRAND (bertrand@lirmm.fr) 3 11/12/2011

Amplificateur source commune : Corrigé

1 / Polarisation

a) Dimensionnement de M

3

et M

4

On écrit que les courants I

D3

et I

D4

sont égaux en valeur absolue :

d'où :

Comme, on a :

On peut écrire :

Pour minimiser la surface, on choisit :

b) Calcul des courants

c) Polarisation de M

1

Il faut déterminer le V

GS1

qui assure dans M

1

le même courant que dans M

2

. Comme ici on a

V

tn

= |V

tp

| et λ

n

= λ

p

= λ, pour V

DS1

=V

DS2

=V

DD

/2, les termes correctifs en (1+λV

DS

) sont les

mêmes pour M

1

et M

2

.

d'où :

Faculté des Sciences, UM2 GMEE102 2011/2012

Yves BERTRAND (bertrand@lirmm.fr) 4 11/12/2011

f) Paramètres g

m

et g

o

des transistors

On utilise les expressions démontrées en cours :

d) Simulation

Amplificateur SC etude polarisation

.model NMOS NMOS vto=1 kp=20e-6 lambda=0.01 level=1

+tox=200e-10 cgdo=200e-12 cgso=200e-12

.model PMOS PMOS vto=-1 kp=10e-6 lambda=0.01 level=1

+tox=200e-10 cgdo=200e-12 cgso=200e-12

M1 2 1 0 0 NMOS W=100u L=10u

M2 2 3 100 100 PMOS w=100u L=10u

M4 3 3 0 0 NMOS W=10u L=10u

M3 3 3 100 100 PMOS w=80u L=10u

VDD 100 0 5

Vin 1 0 1.707

.op

.end

Résultats (dans "Output file"):

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 1.7070 ( 2) 2.8464 ( 3) 2.9968 ( 100) 5.0000

La grille du transistor M2 (nœud 3) est bien polarisée à 3V.

**** MOSFETS

NAME M1 M2 M4 M3

MODEL NMOS PMOS NMOS PMOS

ID 5.14E-05 -5.14E-05 4.11E-05 -4.11E-05

VGS 1.71E+00 -2.00E+00 3.00E+00 -2.00E+00

GM 1.45E-04 1.02E-04 4.11E-05 8.19E-05

GDS 5.00E-07 5.03E-07 3.99E-07 4.03E-07

Les comparaisons entre calculs et simulations sont résumées dans le tableau. La concordance

est tout à fait satisfaisante. Les différences sont essentiellement dues au fait que, pour le calcul

des courants, on néglige le terme correctif 1+λ.V

DS

qui traduit l' effet de la tension drain-

source.

Faculté des Sciences, UM2 GMEE102 2011/2012

Yves BERTRAND (bertrand@lirmm.fr) 5 11/12/2011

M1 M2 M3 M4

Calcul Simul Calcul Simul Calcul Simul Calcul Simul

|I

D

| (

µ

A) 50,0 51,4 50,0 51,4 40,0 41,1 40,0 41,1

g

m

(

µ

A.V

-

1

) 141 145 100 102 80,0 81,9 40,0 41,1

g

o

(

µ

A.V

-

1

) 0,500 0,500 0,500 0,503 0,400 0,403 0,400 0,399

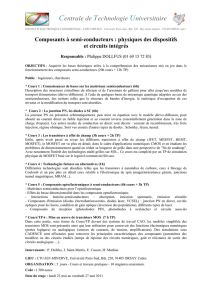

2 / Régime dynamique

a) Schéma équivalent basses fréquences

G

1

S

1

, S

2

, G

2

D

1

, D

2

g

m1

v

gs1

r

01

v

i

=v

gs1

r

02

v

o

b) Résistance de sortie R

out

et gain en tension A

V

La résistance de sortie est la mise en parallèle des résistances de sortie des deux transistors :

Gain en tension

La tension de sortie v

o

est la chute de tension dans r

o1

//r

o2

traversé par le courant -g

m1

v

i

:

c) Simulation

On rajoute simplement 3 lignes au fichier précédent.

.dc Vin 1.5 2 0.001

.tf v(2) Vin

.probe

La caractéristique de transfert est donnée ci-dessous :

On vérifie que la tension de polarisation de la grille de M1, Vi=1,707V est bien située dans le

domaine de transition abrupte de la courbe de transfert (la pente de la courbe correspond au

gain en tension petit signaux).

Vin

1.50V 1.55V 1.60V 1.65V 1.70V 1.75V 1.80V 1.85V 1.90V 1.95V 2.00V

V(2)

0V

1.0V

2.0V

3.0V

4.0V

5.0V

6

6

7

7

8

8

1

/

8

100%