Microélectronique

EISI

MICROELECTRONIQUE EXPOSE

EISI / GH Page: MEL.1

St-Imier, le 10 novembre 2000 [uelec.doc]

Microélectronique

TABLE DES MATIÈRES

1. Introduction ________________________________________________________3

1.1 Définition ______________________________________________________________ 3

1.2 Bref historique __________________________________________________________ 3

1.3 Les étapes de la conception d’un circuit intégré _______________________________ 3

2. Organisation du cours ________________________________________________4

3. Les transistors MOS__________________________________________________5

3.1 Rappel ________________________________________________________________ 5

3.2 Principe de fonctionnement du MOS à enrichissement___________________________ 7

3.3 Caractéristiques du MOS__________________________________________________ 8

3.4 Modèles du MOS ________________________________________________________ 9

3.5 Modèle pour les régimes continu et transitoire _______________________________ 10

3.6 Modèle pour accroissement_______________________________________________ 11

3.7 Modèles SPICE niveaux 1 à 4 (brève description) _____________________________ 12

4. Aperçu de la technologie CMOS_______________________________________13

4.1 Introduction ___________________________________________________________ 13

4.2 Transistor MOS à canal n ________________________________________________ 14

4.3 Transistor MOS à canal p ________________________________________________ 15

4.4 Transistors CMOS ______________________________________________________ 16

5. Circuits de base ____________________________________________________18

5.1 Inverseur _____________________________________________________________ 18

5.2 Porte de transmission ___________________________________________________ 19

5.3 Miroir de courant_______________________________________________________ 20

5.4 Source de courant Wilson ________________________________________________ 21

5.5 Source de courant cascode _______________________________________________ 22

5.6 Paire différentielle______________________________________________________ 22

5.7 OTA (Operationnal Transconductance Amplifier) _____________________________ 23

5.8 Mise en série et en parallèle de MOS _______________________________________ 24

EISI

MICROELECTRONIQUE EXPOSE

EISI / GH Page: MEL.2

St-Imier, le 10 novembre 2000 [uelec.doc]

5.9 Portes NAND et NOR____________________________________________________ 25

5.10 Porte OU-EXCLUSIF____________________________________________________ 26

5.11 Bascule D_____________________________________________________________ 26

5.12 Notion de cellule _______________________________________________________ 27

EISI

MICROELECTRONIQUE EXPOSE

EISI / GH Page: MEL.3

St-Imier, le 10 novembre 2000 [uelec.doc]

1. INTRODUCTION

1.1 Définition

La micro-électronique consiste en la réalisation miniaturisée de fonctions

électroniques de plus en plus complexes sur un seul support (du silicium en

général).

Au départ, le but de la micro-électronique était la réduction du poids et du

volume des appareils, mais ces deux critères sont devenus secondaires face à

l’amélioration de la fiabilité et la réduction du prix de revient que permet

l’intégration. Pour ces diverses raisons, la micro-électronique connaît une

expansion industrielle exceptionnelle puisque l’on peut estimer que, depuis

1963, la production double tous les ans.

1.2 Bref historique

• Depuis 1920 environ, les applications industrielles de l’électronique (la

T.S.F. à l’époque) nécessitent une diminution du poids et du volume des

appareils.

• En 1947 le premier transistor bipolaire est réalise par un groupe de

recherche des Bell Laboratories.

• En 1955 réalisation industrielle du transistor.

• Très vite, divers microassemblages de dispositif semi-conducteurs sont

étudiés pour arriver en 1958 au premier circuit intégré qui comportait,

dans un même bloc de silicium, un transistor, quatre diodes et quelques

résistances.

• Une année plus tard, en 1959, le Dr. Noyce met au point la méthode

planar. Bien qu’initialement mise au point pour les circuits discrets, cette

méthode peut être considérée comme à l’origine du développement

industriel des circuits intégrés.

1.3 Les étapes de la conception d’un circuit intégré

Afin de bien comprendre le rôle des divers outils informatiques utilisés en

microélectronique, il importe de bien saisir les principales étapes qui

interviennent dans la réalisation d’un circuit intégré.

Après avoir défini un cahier des charges précis, la première étape consiste à

réaliser un schéma électrique qui satisfasse aux exigences. On parle de

EISI

MICROELECTRONIQUE EXPOSE

EISI / GH Page: MEL.4

St-Imier, le 10 novembre 2000 [uelec.doc]

conception du circuit et, dans cette phase, l’approche de l’ingénieur diffère

quelque peu de celle utilisée en électronique discrète. En effet, on ne peut

tester un circuit intégré qu’après l’avoir intégré (!). Il n’est donc pas

possible, pour des raisons de coût et de temps, de réaliser divers prototype et

de les tester avant d’arriver au produit fini. Pour cette raison, l’ingénieur va

remplacer le développement de prototypes par une série de simulations sur

ordinateur. On voit donc ici tout l’importance d’avoir un simulateur de

circuits électriques qui soit précis tant dans le calcul des phénomènes que

dans la modélisation des paramètres électriques.

L’étape suivante consiste à dessiner le circuit intégré. Cette opération

consiste à définir l’emplacement et les dimensions des éléments. Elle se fait en

dessinant différents masques qui seront utilisé par le fabricant de circuit

intégré (fondeur). De plus, il importe de vérifier très soigneusement la

parfaite adéquation entre le schéma électrique et le dessin des masques. Pour

cette étape également, un outil CAO est indispensable.

Après intégration, le circuit doit être testé et, suivant sa complexité, cette

opération nécessite également l’usage d’un outil informatique.

2. ORGANISATION DU COURS

L’enseignement de la microélectronique comporte une partie théorique

(résumée dans ce chapitre) et une partie pratique dans laquelle chaque

étudiant ingénieur réalise une partie d’un circuit intégré « gate-array ».

Il est évidemment impossible de parler de microélectronique sans faire

référence à l’électronique et, plus particulièrement, au transistor MOS qui

sera utilisé lors de ce cours. Dans le paragraphe 3, on rappelle les bases

essentielles du fonctionnement des MOS et de la technologie CMOS. De plus,

différents modèles du MOS sont présentés. Le paragraphe 4 présente un

aperçu de la technologie CMOS. Les circuits de base de la microélectronique

sont présentés dans le chapitre 5.

EISI

MICROELECTRONIQUE EXPOSE

EISI / GH Page: MEL.5

St-Imier, le 10 novembre 2000 [uelec.doc]

3. LES TRANSISTORS MOS

3.1 Rappel

Le transistor MOSFET ("Metal Oxide Semiconductor Field Effet Transistor")

appelé également MOST ou simplement MOS ressemble, par son principe de

fonctionnement, au JFET. Dans ce type de transistor, la grille ne forme pas

une jonction avec le canal drain-source (comme dans le cas du JFET) mais est

isolée de celui-ci par un dépôt d'oxyde de silicium.

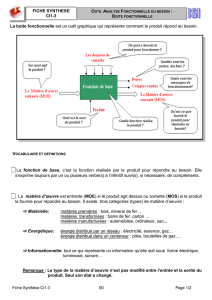

Deux structures sont envisageables (Fig. 3.1); l'une se rapproche de celle du

JFET (Fig. 3.1a), on parle alors de MOS à appauvrissement ("depletion

mode"). L'autre structure diffère quelque peu de celle du JFET (Fig. 3.1b), on

parle dans ce cas de MOS à enrichissement ("ehancement mode"). Les deux

structures ci-dessus peuvent, bien entendu, être réalisées en canal n ou p ce

qui donne quatre types de MOS. (cf. chapitres 2 et 3 du cours d’électronique)

Fig. 3.1

métal

métal

diffusion n+

diffusion n+

substrat p

substrat p

drain

drain

grille

grille

source

source

oxyde de

silicium

oxyde de

silicium

polysilicium

polysilicium

a) MOS à appauvris-

sement canal n sur

substrat p

b) MOS à enrichissement

canal n sur substrat p

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

1

/

28

100%