T - Electronique

! "! #!

Table des matières

Chapitre I:

! "! #! $

I.1 %&&'&(&)$

I.2 %&&'&( &)*$

I.3 %&&(&)+

I.4 %&&( &)*,

I.5 -&.

I.5.1 )&.

I.5.2 )/&&!**#0

I.6 1'&'

I.7 *&'

I.8 !$$$2

I.8.1 &#!34

I.8.2 &&'$

%#!#!!5

II.1 &&&&65

II.2 &&7&65

II.3 .

II.3.1 780

II.4 !&&'0

II.4.1 &&7&2

II.4.2 76&&4

II.4.3 1'&'$

II.5 !&&#)&&,

II.5.1 18&&,

II.5.2 3*9:;

"#

<;

!=

5

II.5.3 9:;

"#

>;

!=

5

Chapitre III: ?## !#"@#.

III.1 &9'1&&*-&:.

III.2 A&A6*20

III.3 &&20

III.4 ?!!9!&&!&&*:22

III.4.1 ;&A!!22

III.4.2 A22

III.4.3 #!!&24

III.4.4 1/*&A!!#2$

III.4.5 '2+

III.4.6 6&2+

III.4.7 &&2,

III.4.8 #9?:2,

III.4.9 2,

III.4.10 6&&&25

III.4.11 !&*25

III.4.12 %&)&19:25

III.4.13 %)&2&9-&:2.

III.4.14 %)!**#2.

III.4.15 ;!!#B7!!-#40

2

III.4.16 ;!!C%C#B7!!-#4

III.4.17 ;&!!1##4

III.4.18 ;!!-?!!?&4

III.4.19 %A&7&*'4

III.4.20 &&&A!!4

III.5 &?a#:42

III.5.1 #400042

III.5.2 %*4$

III.5.3 #=*&#=(=!(==!45

III.5.4 &&7&&*&#=#45

III.5.5 !*3#3!3!4.

III.5.6 ?&C1*$

III.5.7 %&&&&A&*&$

Chapitre IV: !#3! ###$2

IV.1 &/&$2

IV.1.1 /619:$2

IV.1.2 /6$2

IV.1.3 //$$

IV.2 &/&$$

IV.2.1 /4$$

IV.2.2 &&$+

IV.2.3 //$+

IV.3 &&$,

IV.3.1 &$,

IV.4 &&$.

IV.4.1 &)*$.

IV.4.2 )+0

IV.4.3 &+0

IV.5 *9:+

IV.6 &3-,&*&+

IV.6.1 %*&AA&+2

IV.6.2 %*&AA&+2

IV.6.3 %*&AA&+4

IV.6.4 3-,&*&+4

Chapitre V: !##@!###++

V.1 &3&&++

V.1.1 3& #++

V.1.2 3& #=++

V.1.3 3&DEDE=++

V.1.4 3&*&&&A8*+,

V.1.5 3&DE*&&A&+,

V.1.6 /?+5

V.1.7 3& #F&1+5

V.1.8 3&DEF&1+.

V.1.9 3&+.

V.1.10 &&AG*%&+.

V.2 &*&&,0

V.2.1 &*&&)&A&,0

V.2.2 & *&&&,

V.3 &*&&)*,

4 ! "! #!

V.3.1 *&&)*H&H,

V.4 &&,2

V.4.1 &&&7&,2

V.4.2 &&&7&,4

V.4.3 &&I&&7&,$

V.4.4 *,+

V.4.5 &&&&&7,+

V.4.6 &&,,

Chapitre VI: # #5

VI.1 &AA&7&5

VI.1.1 11 5

VI.1.2 5

VI.1.3

!% " 3

% 5

VI.1.4 *'% 52

VI.1.5

!??J3

% 52

VI.1.6 ?#=52

VI.1.7 &61152

VI.1.8 *&54

VI.1.9 76115$

VI.1.10 6 5+

VI.1.11 6% 5,

VI.1.12 6% % 55

VI.2 *&55

VI.2.1 65.

VI.2.2 &'F5.

VI.2.3 *&&&&'F&5.

$

Chapitre I: LE CIRCUIT RC EN REGIME TRANSITOIRE

I.1 Circuit RC Passe bas, réponse à un échelon

6**6

&6&&A&1

τ

t

0

e)VV(V)t(V

−

∞∞

−−=

&&;∞K(;K0(τK &&

)e1(E)t(V

t

s

τ

−

−=

τ&&&*;&+2L

&1A(

AAVs(

τ

) = E(1-e-

τ

/

τ

) = E(1-1/e) = 0,63E

I.2 Circuit RC Passe bas, Réponse à un

rectangle

• ∈M(M⇒*

;&9:K9--Iτ:9

*&:

• >⇒*;

&

K;

-Iτ

9*&:;

K9--!Iτ:

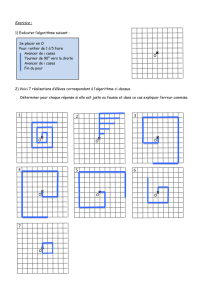

Exercice : 1)

&H && '& 1 K0B

K00?

&*6&-&&&

&&&*&&&1&/&&'&

?*- &)6

&&'&

?*- &)*6

&&'&

0;

-

$;

2&

&

;

;&

;

;

!

K0

;&

K0

;

;&

;

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

1

/

90

100%

![III - 1 - Structure de [2-NH2-5-Cl-C5H3NH]H2PO4](http://s1.studylibfr.com/store/data/001350928_1-6336ead36171de9b56ffcacd7d3acd1d-300x300.png)